众所周知,setup和hold作为timing分析与验证中最重要的概念之一,是时序电路正常工作必须满足的条件。

但是很多初学者甚至某些工作数年的工程师,对时序电路需要验证setup和hold背后的原理可能并不清楚。

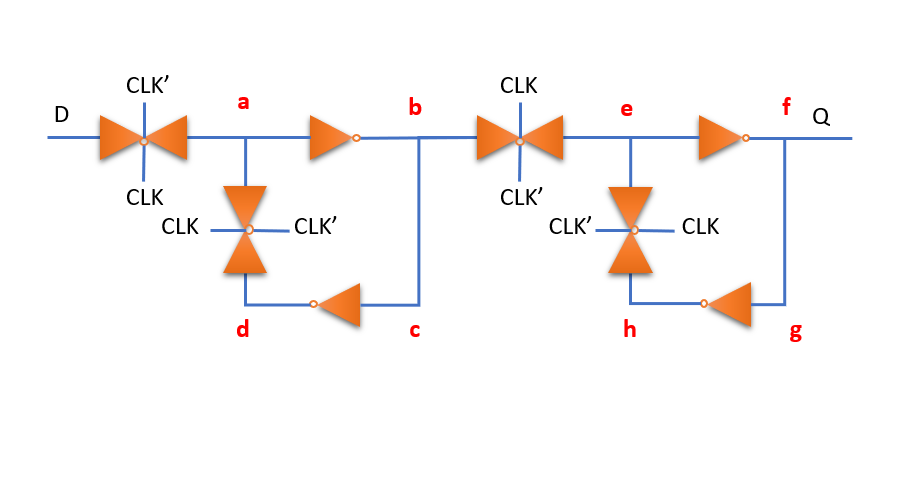

下图是上升沿触发的D触发器的一种典型的基于传输门的设计原理:

首先我们先把注意力集中在电路的前半部分。

假设CLK的初始状态为0,此时第一个传输门导通,信号走向为:

D -> a -> b -> c -> d 注:路径1

从以上信号走向可以看出,信号必须在CLK上升沿到来之前在d点保持稳定,否则如果在这之前D pin的信号发生变化,就会导致DFF锁住错误的信号。换句话说,如果假设路径1需要花费的时间为t0,那么D处的信号必须要在CLK上升沿之前的t0或更早的时间内保持稳定。此即setup的物理意义,也是timing report种library setup time所代表的含义。

接着,当CLK从0变成1后,D与a之间的传输门关闭,a与d之间的传输门导通,此时信号走向为:

d -> a -> -> b -> e -> f(Q) -> g -> h

需要注意的是,当信号从0变为1的过程中,在一段很短的时间内,所有传输门都可能导通,若此时D端信号发生变化而CLK的transition比较慢,则会发生新值覆盖旧值而导致信号错误的现象。因此,D段信号需要在传输门完成开/关过程中保持稳定,此即为hold的物理意义,也是timing report中library hold time代表的含义。