由慢时钟域到快时钟域的脉冲同步电路结构相对简单。慢时钟域的脉冲信号在快时钟域来看就是电平信号。注意跨时钟域同步的时候输出的脉冲必须是寄存器信号,如果需要被同步的脉冲是通过组合逻辑产生的,那么在同步之前一定要在本时钟域下用寄存器抓一拍。比如,clka下通过计数器产生了脉冲信号pls\_a = (cnt==4’d5),如果要将pls\_a同步到另外一个时钟域,首先在clka下将pls\_a打一拍,避免组合逻辑产生的毛刺,这一点是异步信号处理的基本原则。

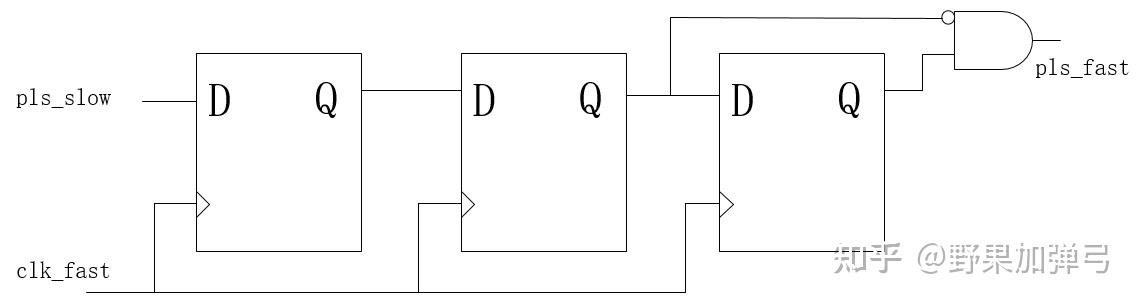

图 慢时钟到快时钟转换电路

如图3所示,pls\_slow是来自慢时钟域的脉冲信号被同步到快时钟域clk\_fast,在pls\_slow经过2级DFF处理后的信号认为是稳定的,将该信号取反并和下一拍的信号作与逻辑,即可在clk\_fast时钟域产生脉冲信号neg\_b(下降沿脉冲检测),同理将该信号与下一拍的取反信号作与逻辑可产生pos\_b(上升沿脉冲检测)。

rtl代码如下所示:

```

verilog

module pls_sync_s2f(

rst_n ,

clka ,

clkb , //fast clk

pls_a , //pluse in clka

neg_b ,

pos_b

);

//parametr

parameter DLY = 1 ;

//input output

input rst_n ;

input clka ;//slow clk

input clkb ;//fast clk

input pls_a ;//pluse in clka

output pos_b ;//posedge pluse in clkb

output neg_b ;//negedge pluse in clkb

//-----------------------------

//--signal

//-----------------------------

reg dff1 ;

reg dff2 ;

reg dff3 ;

//-----------------------------

//--main circuit

//-----------------------------

always@(posedge clkb or negedge rst_n)

begin

if(!rst_n) begin

dff1 <= 1'b0 ;

dff2 <= 1'b0 ;

dff3 <= 1'b0 ;

end

else begin

dff1 <= #DLY pls_a ;

dff2 <= #DLY dff1 ;

dff3 <= #DLY dff2 ;

end

end

assign pos_b = dff2 & (~dff3) ;

assign neg_b = (~dff2) & dff3 ;

endmodule

~~~

```

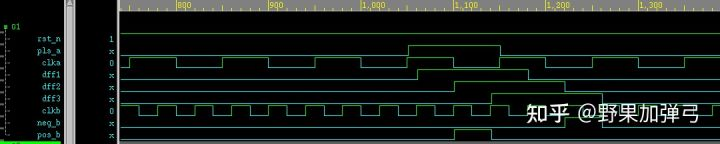

仿真波形如图