http://www.elecfans.com/d/1284779.html

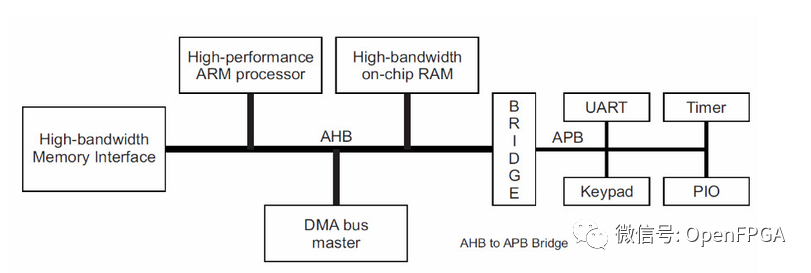

在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。AMBA规范主要包括了**AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。**

AMBA 2.0规范包括四个部分:AHB、ASB、APB、AXI和[Te](http://www.elecfans.com/tags/te/)st Methodology。

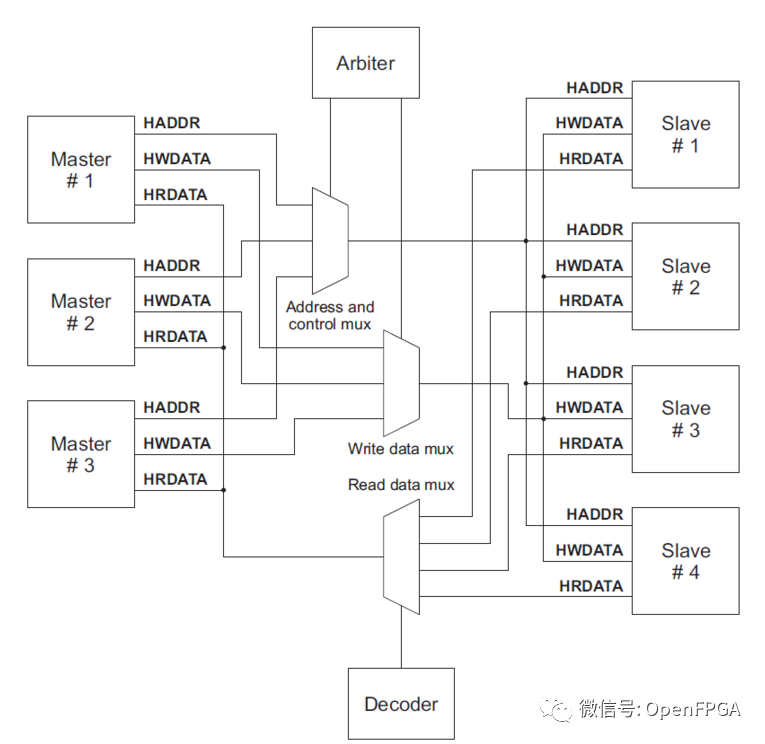

**AHB的相互连接采用了传统的带有主模块和从模块的共享总线**

[接口](http://www.hqchip.com/app/1039)与互连功能分离,这对芯片上模块之间的互连具有重要意义。**AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。**

AMBA协议的演进

* ·AMBA 1 只有ASB和APB协议;

* ·AMBA 2 引入AHB协议用于高速数据传输;

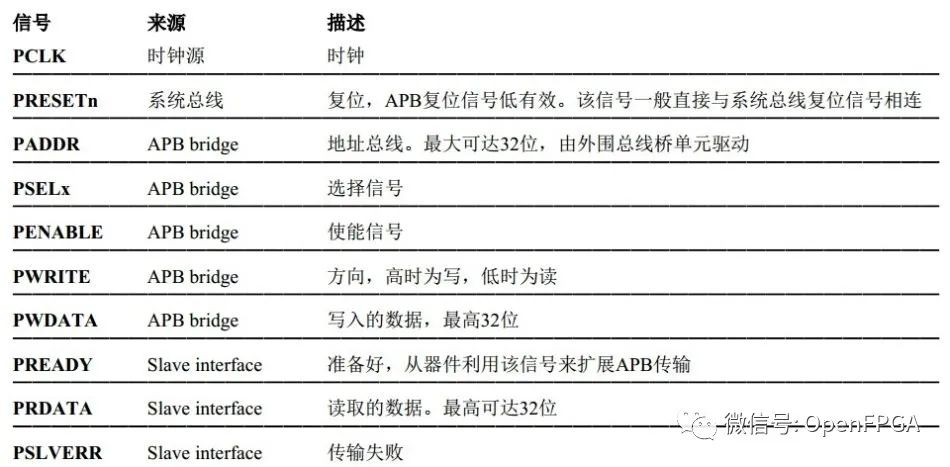

* ·AMBA 3,为适应高吞吐量传输和调试引入AXI和ATB,增加高级可扩展接口,而AHB协议缩减为AHB-lite,APB协议增加了PREADY和PSLVERR,ASB由于设计复杂而不再使用;

* ·AMBA 4,AXI得到了增强,引入QOS和long burst的支持,根据应用不同可选AXI4,AXI4-lite,AXI4-stream,同时为满足复杂SOC的操作一致性引入ACE和ACE-lite协议,APB和ATB也同时得到增强,比如APB加入了PPROT和PSTRB,另外为改善总线数据传输引入QVN协议; ·适应更加复杂的高速NOC设计,引入环形总线协议,推出的AMBA CHI协议。

*

V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。APB的协议也十分简单,甚至不是流水的操作,固定两个[时钟](http://www.hqchip.com/app/1045)周期完成一次读或写的操作。其特性包括:两个时钟周期传输,无需等待周期和回应信号,控制逻辑简单,只有四个控制信号

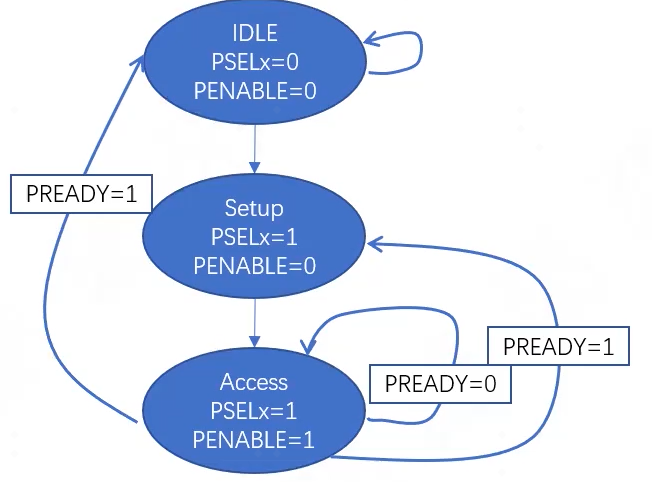

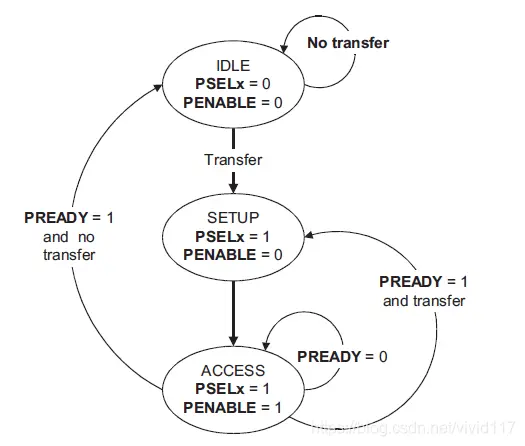

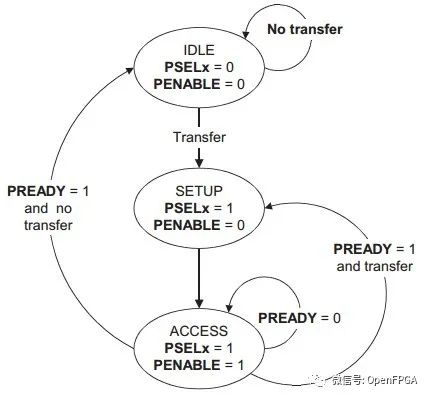

系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。 ·当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。 ·系统进入ENABLE状态时,维持之前在SETUP 状态的[PAD](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)DR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

V2.0 AHB是第二代AMBA协议最重要的一部分。AHB总线规范是AMBA总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral 周围的,周边的 Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速[RAM](http://www.elecfans.com/tags/ram/)、NAND FLASH、[DMA](http://www.elecfans.com/tags/dma/)、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。

相比于APB,区分了地址周期和数据周期。 AHB总线强大之处在于它可以将微控制器([CPU](http://www.elecfans.com/tags/cpu/))、高带宽的片上RAM、高带宽的外部[存储器](http://www.hqchip.com/app/724)接口、DMA总线控制器,以及各种AHB接口的控制器等连接起来构成一个独立的完整SOC系统,还可以通过AHB-APB桥来连接APB总线系统。

## **arbiter** 仲裁人

通过AHB-APB桥来连接APB总线系统 AHB总线由主设备Master、从设备Slave,内部包括仲裁器,译码器,数据多路和地址控制多路组成。 ·主设备发起一次读/写操作,某一时刻只允许一个主设备使用总线。 ·从设备响应一次读/写操作,通过地址映射选择使用哪一个从设备。 ·仲裁器允许某一个主设备控制总线 ·译码器通过地址译码决定选择哪一个从设备 仲裁机制 仲裁机制保证了任意时刻只有一个master可以接入总线。arbiter决定哪个发出接入请求的master可以接入总线,这通过优先级算法实现。AHB规范并没有给出优先级算法,设计者需要根据具体的系统要求定义。一般情况下arbiter不会中断一个burst传输,将总线接入权让给其他master。当然未定义长度的burst传输是可以打断的,这要看优先级算法是如何规定的。如果一笔burst被打断,master再度获得接入权限时,会传递剩余的部分。如一笔长度为INCR8的传输在传递3 beat后被打断,master再次获得接入授权后,会继续传输剩余的5 beat,剩余部分可以由一个SINGLE和一个INCR4组成,或者一个INCR。 地址译码器 地址译码器用于为总线上每个slave提供选择信号HSELx,选择信号是通过组合逻辑对地址码译码产生的。只有当前的数据传输完成后(HREADY为高),slave才会采样地址和控制信号以及HSELx。在一定条件下可能会出现这样的情况:产生HSELx信号而HREADY为低,在当前传输后slave会改变。每个slave最小的地址空间为1KB,所有的master的burst传输上限也是1KB,如此设计保证了不会出现地址越界问题。当一个设计不会用到所有的地址空间时,可能出现访问到一个不存在的地址的情况,这就需要增加一个附加的默认slave来为上面的情况提供一个响应。当SEQ或NONSEQ传输访问到一个不存在的地址,默认slave应该提供ERROR响应;当IDLE或BUSY传输访问到一个不存在的地址,默认slave会响应OKAY。地址译码器会带有实现默认slave的功能。

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced[Mi](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)crocontroller Bus Architecture)3.0协议中最重要的部分。 ·高性能、高带宽、低延迟的片内总线 ·地址/控制和数据相位是分离的,分离的读写数据通道。控制和数据通道分离,就可以不等需要的操作完成,就发出下一个操作,流水线操作,数据吞吐量增加达到提速的作用。 ·单向通道体系结构,使得片上信息流只是以单方向传输,减少了延时,更小的面积,更低的功耗,获得优异的性能。 AXI4 是第四代AMBA协议重要的一部分,AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-streamAXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在[FPGA](http://www.elecfans.com/tags/fpga/)进行以数据为主导的大量数据的传输应用。 · 适合高带宽低延时设计,无需复杂的桥就实现高频操作,向下兼容已有的AHB和APB接口。 ·分离地址/控制、数据相位 ·分离的读写数据通道,提供低功耗DMA ·使用字节线支持非对齐的数据传输 ·使用基于burst的传输,只需传输首地址 ·支持多种传输方式,支持乱序传输 ·允许容易的添加寄存器来进行时序收敛 AXI架构分为5个独立的传输通道,读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。数据总线可为(8/16/32/64/128/256/512/1024bit),最大为单次传输一个字节的数据。