## 1.1 背景介绍

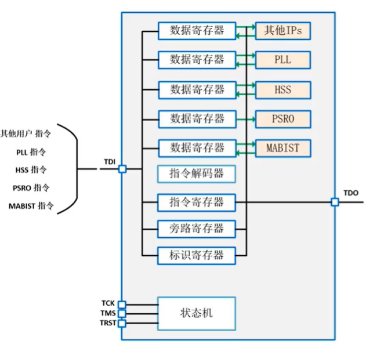

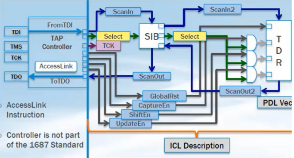

* JTAG框架

1. 基本目标:实现芯片间互联线的测试

2. 扩展功能:实现芯片内各种IP的调试

* 通过TDR(数据寄存器)操纵和观测IP

* 通过指令集激活某一个IP的TDR

* JTAG缺点

1. 1. 片上IP数量导致JTAG指令集的增加

2. 片上IP数量导致指令解码器变得非常复杂

3. 广播架构不利于PR

4. 测试模式在芯片设计阶段固定下来,缺乏灵活性

5. JTAG标准并未定义TDR如何操纵IP,而是使用document描述指导施加激励与获取结果的过程

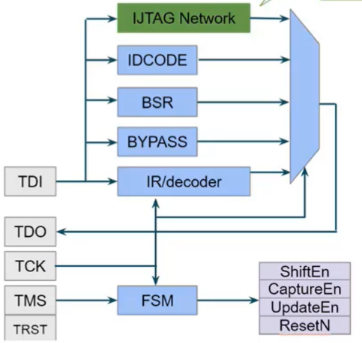

## 1.2 IJATG架构

* IJTAG完全兼容JTAG网络

* 描述TDR到TAP之间的网络结构

* 串行TDR链路,通过SIB灵活配置

* 规范了TDR和IP之间的交互语言

* 即插即用

### 1.2.1 IJTAG标准

* IEEE 1687 Standard

* 2005年起草,2014年颁布,众多IC/EDA公司参与

* 包含三个部分:

* 灵活的串行TDR链路,用以测试片上IP

* IJTAG网络连接语言:ICL(Instrument Connectivity Language),描述整个IJTAG网络结构

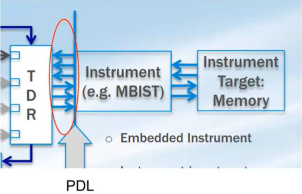

* IJATG程序描述语言:PDL(Propcedural Description Language),描述TDR与IP之间的交互

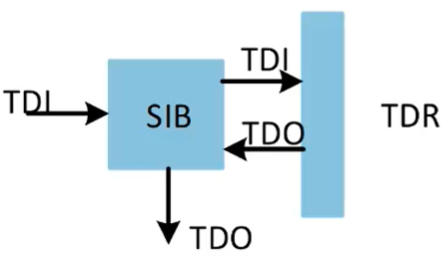

# 2 SIB的结构

## 2.1 SIB概念

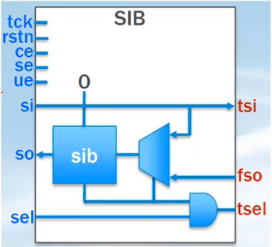

1. SIB:Segment-insertion-Bit

2. SIB是单比特的TDR

3. SIB有开和关两种状态

4. 插入SIB来实现任意层次化结构

5. 利用SIB可以实现对IJTAG网络的灵活配置

## 2.2 SIB的结构

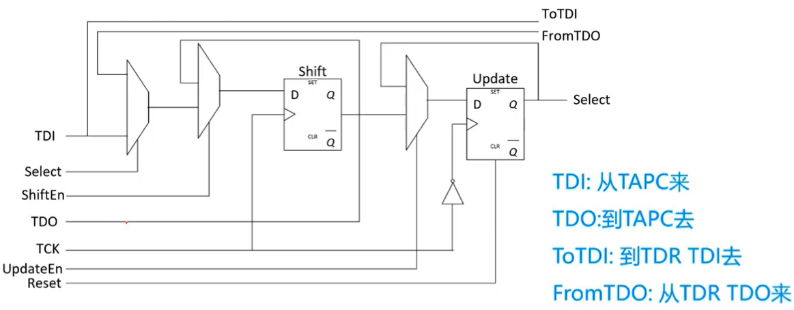

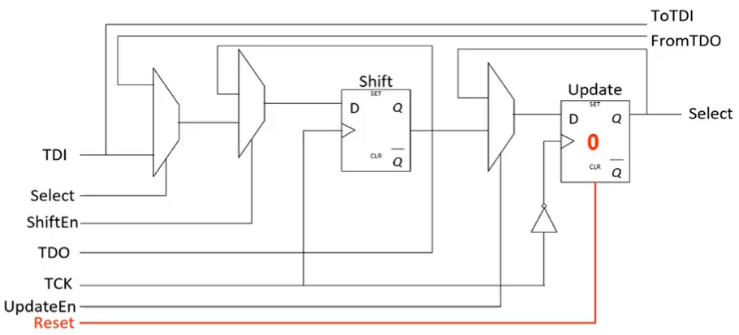

### 2.2.1 总体结构

* ShiftEn打开,TDI经过两个选择器经过Shift寄存器,最终到达TDO,数据不进入下一级SIB;

* ShiftEn打开,UpdateEn打开,TDI输入后经过Shift寄存器、Update寄存器,最终Select影响输入部分的Select信号(我理解两个select信号为同个端口),Select打开后,数据可进入下一级SIB。路径为:TDI→ToTDI→FromTDO→经过Shift寄存器→TDO;

### 2.2.2 RESET:关闭到下一级SIB网络入口

* 除了上述说到的关闭打开Update寄存器外,还可以使用Reset信号对Update寄存器进行复位;

* 复位信号打开后,TDI输入的数据只能经过当前SIB,无法进入下一级SIB网络;

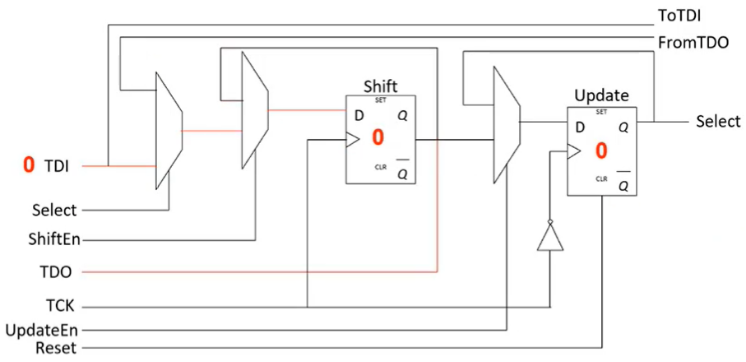

### 2.2.3 Close:关闭到下一级SIB网络的入口

* TDI输入0,Select为0,移位数据进入Shift寄存器,使得Shift寄存器输出为0,然后打开UpdateEn信号,使得Update寄存器输出为0,然后关闭UpdateEn信号,如此使得Update寄存器一直保持0,测试时下一级SIB网络使用不会打开;

* 目的:让该SIB的下一级SIB网络在测试时始终不接入测试;

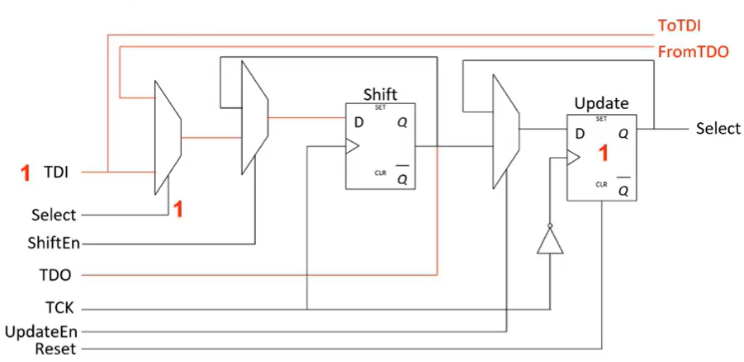

### 2.2.4 Open:打开到下一级SIB网络的入口

* 经过TDI移入1,使得Shift寄存器输出为1,打开UpdateEn信号,使得Update寄存器输出Select信号为1,Select为1后,第一个MUX选择器选择上方通路;

* 数据路径:TDI输入数据→ToTDI(下一级SIB网络)→FromTDO(接收下一级SIB出来的数据)→经过两个MUX和Shift寄存器→TDO输出;

# 3 SIB的网络

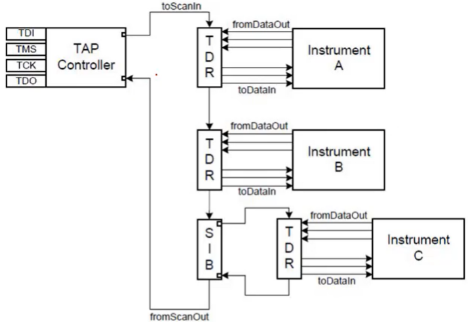

## 3.1 SIB多级网络结构(plug-and-play)

* 通过TDR与SIB的组合,对芯片进行整体测试;

* 上图中,可以看做Level0(2个TDR+SIB),Level1(1个TDR);

* Level0中的两个TDR连接的instrumentA、B一定会被测试到,在shift数据时就需要移入instrumentA、B的测试向量位宽,SIB可以控制后面的TDR与instrumentsC是否需要被测试;

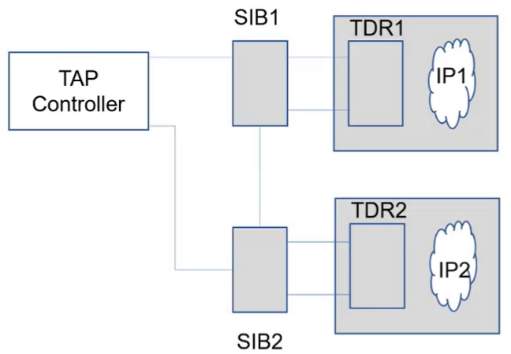

## 3.2 配置SIB的网络结构

* 串联两个SIB;

* 每个SIB后面分别挂一组TDR和instrument;

* TDR1长度为10;

* TDR2长度为5;

* 如何通过TDI扫描数据来配置该网络?

* 激活TDR1

* 激活TDR2

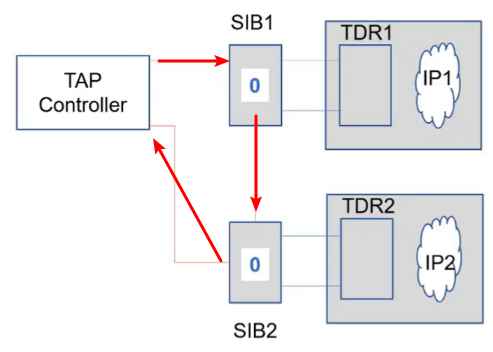

### 3.2.1 系统初始化

RESET状态:

* 移入2bit数据,将SIB1与SIB2状态均置为0;

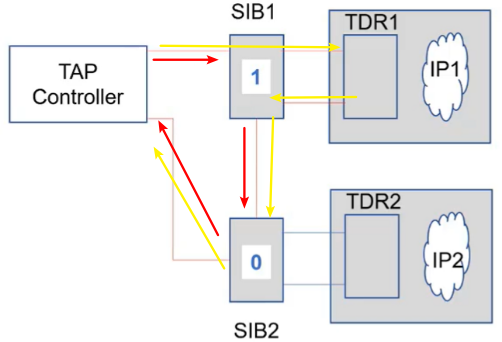

* 步骤一:

* 移入2bit数据,将SIB1置为1,SIB2置为0;(红色箭头)

* 打开Ijtag\_update;

* 激活打开TDR1网络;(黄色箭头)

* 步骤二:

* 移入12bits数据,因为IP1长度10,再加上SIB1、2的两个bit;

* 保持SIB1打开;

* 保持SIB2关闭;

* 操纵TDR1(10bits);

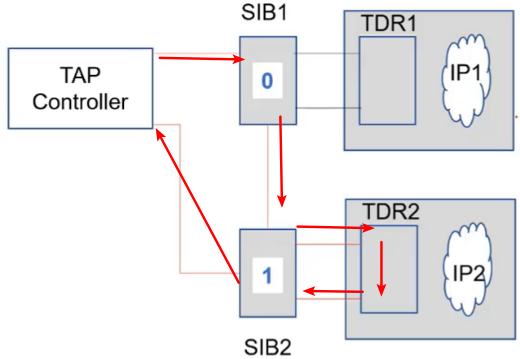

* 步骤三:

* 移入12bit数据,将SIB1置为0,将SIB2置为1;

* 打开Ijtag\_update;

* 关闭TDR1网络,打开TDR2网络;

* 步骤四:

* 移入7bit数据;

* 保持SIB1关闭,保持SIB2打开,操纵TDR2(5bits);

# 4 ICL语法

## 4.1 基本概念

* ICL:Instrument Connection Language;

* ICL描述IJTAG网络的连接关系;

* ICL是可读文件;

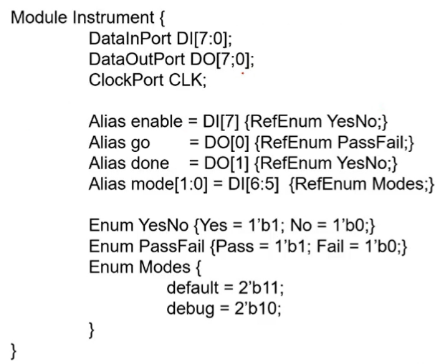

## 4.2 描述Instrument

* Instrument表示该器件的例化名;

* DataInPort DI、DataOutPort DO、ClockPort CLK:描述该模块的对外接口;

* Alias enable表示部分端口的作用,{}内我理解表示有效取值范围;

* Enum用于解释,二进制对应的工作模式;

## 4.3 描述TDR

* 描述TDR的对外接口;

* ScanOutPort SO{Source SR\[0\]}表示SR的第0bit连接至SO;

* ScanRegister SR\[7:0\] {ScanInSource SI}表示SR的位宽10bit,扫描输入的源头是SI;

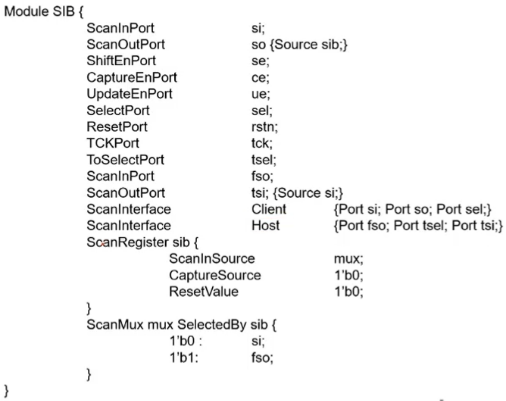

## 4.4 描述SIB

* ScanOutPort so{Source sib;},so的数据源头是sib;

* ScanOutPort tsi;{Source si},对下一级输出端口tsi,源头是si;

* ScanInterface Client {},当前SIB对上一级的接口;

* ScanInterface Host {},当前SIB对下一级的接口;

* ScanRegister sib {},设置sib的输入源,captrue的源头信号,reset的源头信号;

* ScanMux设置sib的Q端口控制MUX的信号输出到sib,Q端为1‘b0,si信号送入sib,Q端为1‘b1,fso信号送入sib;(这部分逻辑较混乱,正确性待考证)

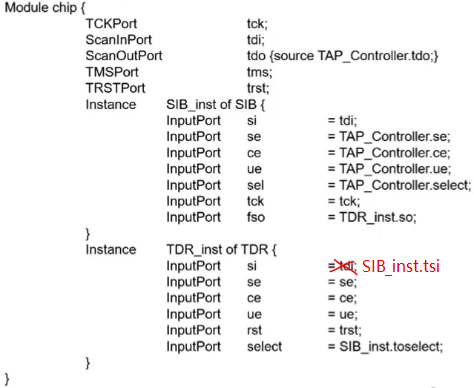

## 4.5 描述chip

# 5 PDL语法

## 5.1 基本概念

* PDL:Procedural Description Language

* PDL描述如何配置和操作片上IP/instrument(如何激励与观测IP)

* EDA工具可以将IP的PDL按照层次结构retargeting到更上一级IJTAG网络指导chip层;

* retargeting:将IP的接口通过PDL逐层的向上MAP到chip的端口上,完成测试;

## 5.2 PDL命令

* iWrite:向对象中写入数据

* iRead:从对象中读取数据

* iApply:执行PDL命令

* iNote:添加注释

* iProc:定义PDL的procedure

* iCall:调用定义好的proc

* iMerge:并行执行多个proc

* iRunLoop:执行指定数目的时钟周期