# DFT笔记 DC/AC mode与Func

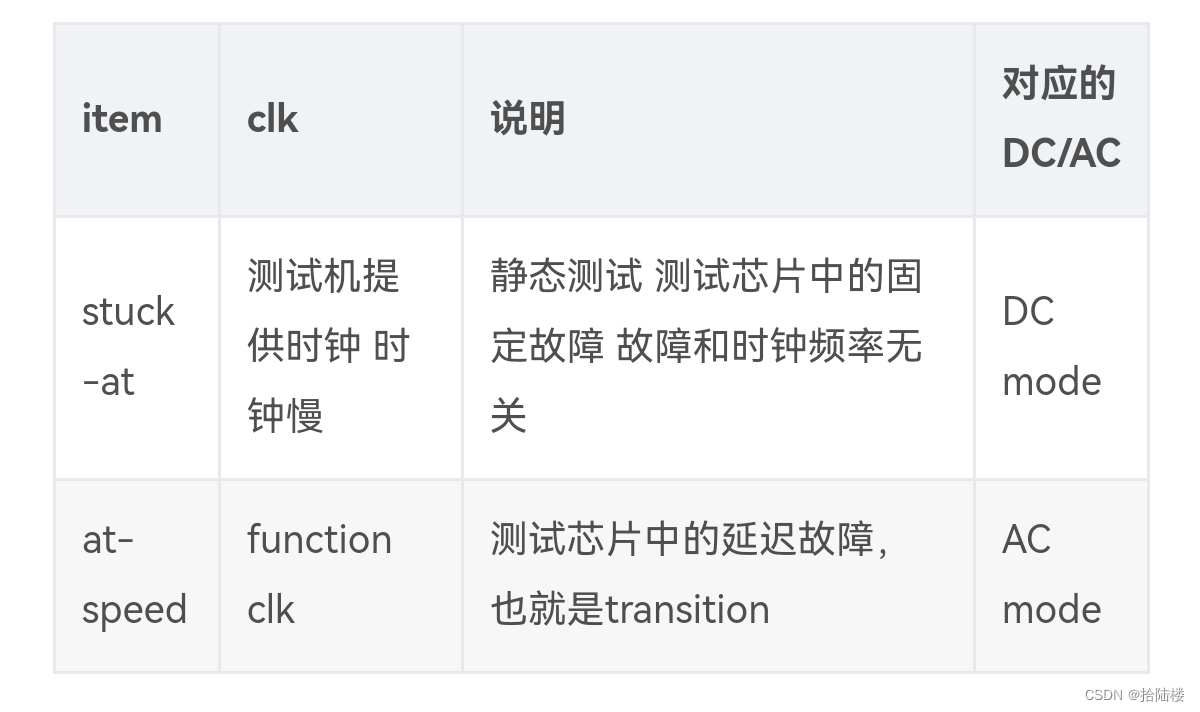

DC模式需要ate测试机台提供test clock时钟(最快100M),DFT工程师需要升级普通reg变成带si和so,se pin的reg,并插入扫描链(scan chain),用于检查设计中尽量多的cell(包括组合逻辑),提高覆盖率是个技术活,需要引入更多的组合逻辑,而且要更多的pattern,pattern是设计中外部输入的值得各种组合。DC模式主要检查设计中stuck at 0和stuck at 1的错误,举例来说,一个与门输入都是1输出必然是1,如果测试出来输出是0,那么就有stuck at 0(SA0)的错误,而输入都是0,得到的结果是1就有SA1的错误。

AC模式下test clock来自pll,也就是func clock同源(频率<=func clock频率),只不过AC模式下,clock从源头出来经过occ电路,再与func clock重叠,此时test clock与func clock在occ电路处有了分别,他们就不是同一个clock,在sdc中,如果区分开,写两个sdc,需要在各自sdc中用set\_case\_analysis设置好mux的输入,用以区分两个clock,也可以不分开,跟mbist一样写到一个sdc里,另外一点区别是ac mode下不检查reg与mem的timing,ac这个模式用来检查data path组合逻辑的transition问题,有些cell低频下功能正常,但制造过程中性能受损,导致高频下transition达不到预期,这也是一种错误。