https://zhuanlan.zhihu.com/p/142377567

**关键词:同步释放,recovery,removal**

在数字IC设计中肯定会涉及到异步复位的问题,因为需要对电路进行复位操作。这种复位设计主要依靠前端设计以及工具来检查,从数字IC后端的角度上讲,只要在timing signoff阶段检查好removal和recovery的check就好。

**Removal timing check**

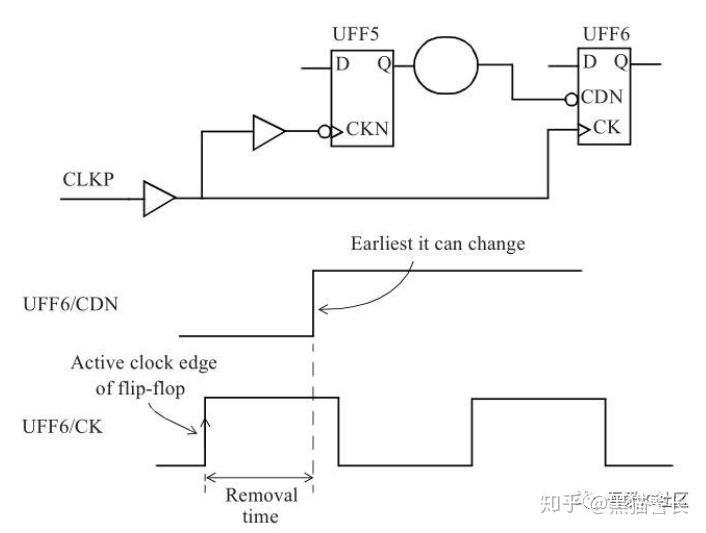

Removal time是指在时钟有效沿来临之后,异步复位信号需要继续保持有效的最短时间。满足这个最短时间才能确保对寄存器进行正常的复位。Removal time check的波形图如下图所示。Removal timing check与hold time check类似。

**Recovery timing check**

Recovery time是指在时钟有效沿到来之前,复位信号保持高电平的最短时间。即复位信号变到非复位状态的电平必须在clk之前一定的时间到达。满足这个Recovery time,可以确保在时钟有效沿来临时,异步复位信号处于无效状态,从而确保正常的数据采样。

从Removal 和Recovery time的定义知道,只要DFF的复位信号不在时钟有效沿附近变化(复位信号远离时钟有效沿),就可以保证电路的正常复位和撤销。

在实际的设计中,比如有的模块是先复位再给模块供应时钟,即保证了复位信号与时钟在时间上是错开的,这种流程可以保证不会出现recovery和removal的问题,因为复位置起撤销时都没有时钟。即使操作流程保证不了,出现recovery和removal违例,由于模块此时都不会工作,也没什么问题。

**同步复位**

复位信号可以理解为一个普通的数据信号,它只有在时钟的跳变沿才会其作用,一般只要复位信号持续时间大于一个时钟周期,就可以保证正确复位。

**异步复位**

复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化。如果异步复位信号跟时钟在一定时间间隔内发生变化,Q值将无法确定,即亚稳态现象。这个时候既是异步复位信号持续时间再长都没有办法,因为不定态已经传递下去。

同步复位虽然解决了当时钟的有效沿来临的时候rst\_n的边沿也正好来临所出现的冒险与竞争。但是从综合的电路上可以看出,多了一个组合逻辑MUX。

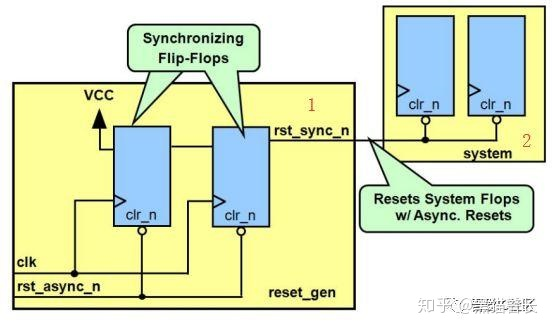

如果设计中所有的复位都是这样的,那会增加很多的资源,导致芯片面积很大。那么有没有更好的解决办法呢?答案是有,那就是**异步复位同步释放机制。**

**异步复位,同步释放**

异步复位,同步释放就是指在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。

- 空白目录

- 流水线

- 流水线性能测评

- 计算机性能测评

- 流水线设计

- 购物车状态机

- 序列检测器

- 序列检测10010

- 序列检测10010带图

- 反相器

- 计数器

- 分频电路

- 偶数分频

- 奇数分频

- 小数分频

- 同步复位异步释放all

- 对的-异步复位同步释放原理

- 同步复位异步释放

- 异步复位为什么要同步释放 ?

- FPGA-异步复位同步释放 通俗解释

- 同步复位

- 状态机

- 状态机的分类

- 状态机5个要素

- FIFO

- 异步fifo中同步为什么要用两级触发器

- 亚稳态

- 亚稳态的产生机理、消除办法 (可以理解为什么打拍)

- 面向对象思想

- 为什么D触发器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自启动

- 毛刺

- 冯诺依曼