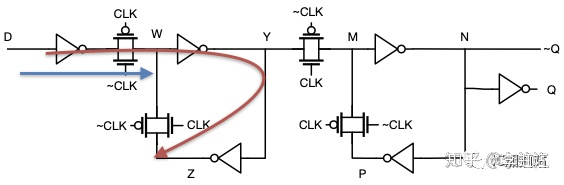

它们与D触发器的内部结构有关系。D触发器的内部是一个主从锁存器(master-slave latch),一个常见的D触发器结构如下图所示

Latch能够存储住状态,靠的是上面的背靠背的反相器。而这个背靠背的反相器能够锁住状态是需要时间的。由此,我们可以分析出

setup time: 在clk的上升沿到来之前,D要传输到Z的时间。因为当Z的值还没有稳定的时候,D如果变化,那么这个背靠背的反相器就无法锁住值。

hold time: 第一个传输门关闭需要的时间,在传输门关闭期间,D->W要保持稳定,这样在传输门关闭之后,W稳定才不会导致背靠背反相器锁住的值发生变化。

所以我们可以看出,当D在setup/hold time window内发生变化,锁存器可能无法锁住一个稳定的值,会发生的结果是

* Q的值可能不是正确的D

* 随着D的变化越靠近时钟沿,Q变稳定的时间越长

* 最后Q稳定到的值可能是随机的

注意我们并不是说Q最后的值不是稳定的1或者0, Q的值最后一定会稳定下来,稳定在高电平或者低电平,这是由于背靠背的反相器会产生正反馈,最终一定会稳定下来。但是当这个稳定的时间超出了clk-to-q的限制,我们就说产生了亚稳态。

- 空白目录

- 流水线

- 流水线性能测评

- 计算机性能测评

- 流水线设计

- 购物车状态机

- 序列检测器

- 序列检测10010

- 序列检测10010带图

- 反相器

- 计数器

- 分频电路

- 偶数分频

- 奇数分频

- 小数分频

- 同步复位异步释放all

- 对的-异步复位同步释放原理

- 同步复位异步释放

- 异步复位为什么要同步释放 ?

- FPGA-异步复位同步释放 通俗解释

- 同步复位

- 状态机

- 状态机的分类

- 状态机5个要素

- FIFO

- 异步fifo中同步为什么要用两级触发器

- 亚稳态

- 亚稳态的产生机理、消除办法 (可以理解为什么打拍)

- 面向对象思想

- 为什么D触发器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自启动

- 毛刺

- 冯诺依曼