https://www.icourse163.org/learn/UESTC-1205788811?tid=1450474442#/learn/content?type=detail&id=1233293349&cid=1252197791

1、偶数分频

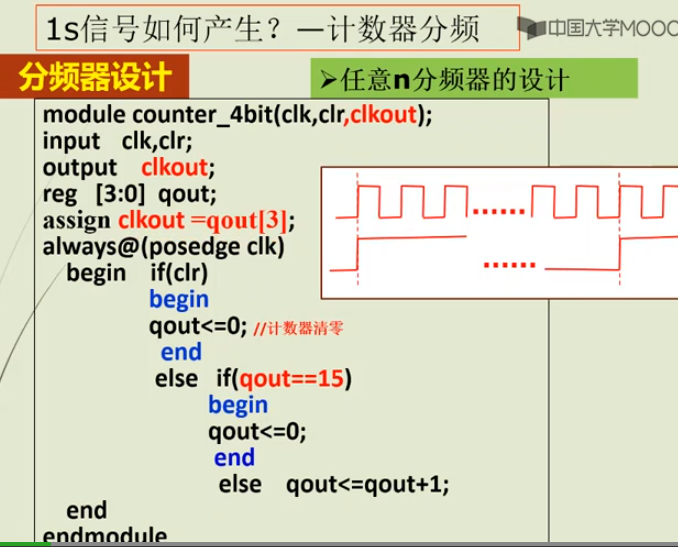

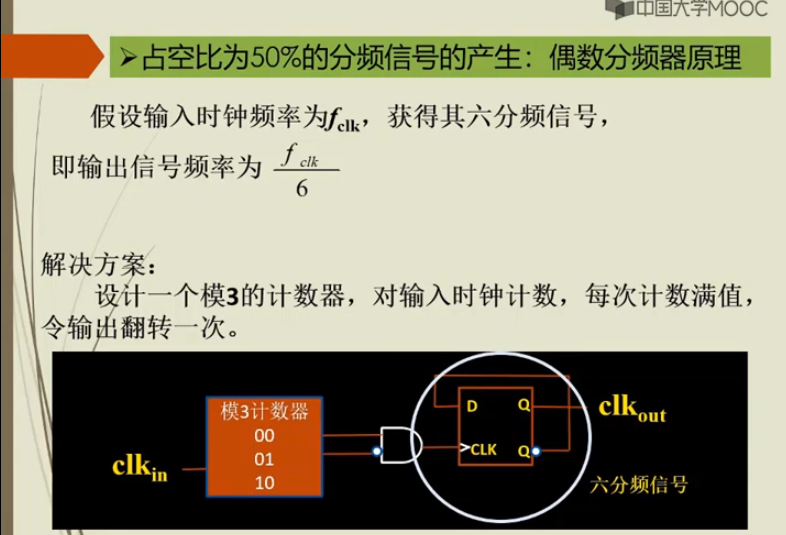

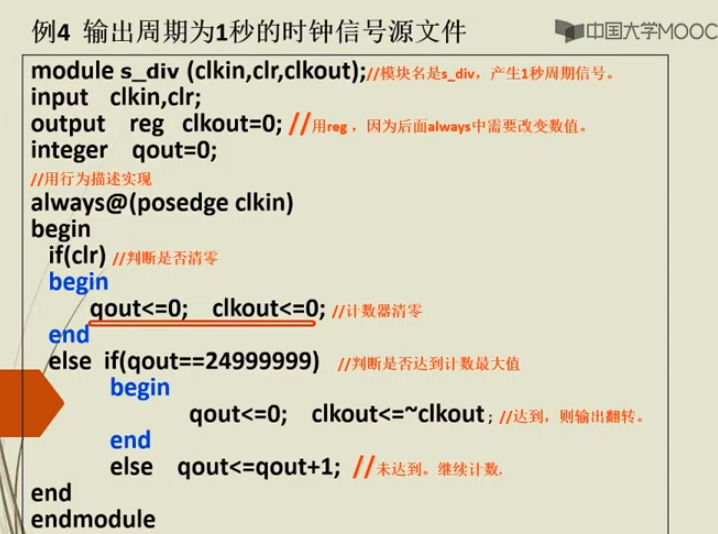

偶数倍分频相对简单,可以通过计数器对预分频的脉冲沿计数实现,如果要进行N倍(N为整数)偶数分频,可由预分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。分频的主体程序如下:

```

module freq_div_even(input clk_in,

input reset,

output reg clk_out

);

reg[2:0] count;

parameter N=8;

always@(posedge clk_in)

begin

if(!reset)

begin

count<=0;

clk_out<=0;

end

else

if(count==(N/2-1))

begin

clk_out<=~clk_out;

count<=0;

end

else

begin

count<=count+1;

end

end

endmodule

```

2、奇数分频

对于对占空比没有特殊要求的奇数分频,需要对上升沿和下降沿脉冲进行计数,利用下降沿产生的波形移相半个输入脉冲的作用,最后用错位“异或”法实现。一个13分频的程序如下:

module count_num(

input clk,

input reset,

output cout//这里是wire型变量

);

reg[4:0] m,n;

reg cout1,cout2;

assign cout = cout1 | cout2//**口诀:模块输入端必须用wire,模块输出端可以用wire,reg,assign必须用wire,always必须用reg**

```

always@(posedge clk)

begin

if(!reset)

begin cout1<=0; m<=0; end

else

begin

if(m=NUM-1)

m<=0;

else

m<=m+1;

if(m<(NUM-1)/2)

cout1<=1;

else

cout1<=0;

end

end

always@(negedge clk)

begin

if(!reset)

begin cout2<=0; n<=0; end

else

begin

if(n=NUM-1)

n<=0;

else

n<=n+1;

if(n<(NUM-1)/2)

cout2<=1;

else

cout2<=0;

end

end

endmodule

```

- 空白目录

- 流水线

- 流水线性能测评

- 计算机性能测评

- 流水线设计

- 购物车状态机

- 序列检测器

- 序列检测10010

- 序列检测10010带图

- 反相器

- 计数器

- 分频电路

- 偶数分频

- 奇数分频

- 小数分频

- 同步复位异步释放all

- 对的-异步复位同步释放原理

- 同步复位异步释放

- 异步复位为什么要同步释放 ?

- FPGA-异步复位同步释放 通俗解释

- 同步复位

- 状态机

- 状态机的分类

- 状态机5个要素

- FIFO

- 异步fifo中同步为什么要用两级触发器

- 亚稳态

- 亚稳态的产生机理、消除办法 (可以理解为什么打拍)

- 面向对象思想

- 为什么D触发器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自启动

- 毛刺

- 冯诺依曼