> assign语句赋值号左边只能是wire类型(只在wire与reg型之中做讨论)。

> always块语句中,被赋值的只能是reg类型。

```

/************************************************************************

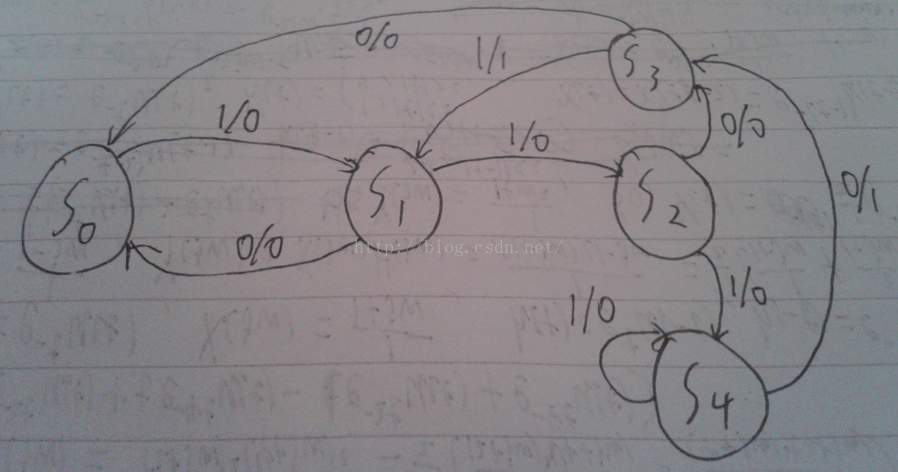

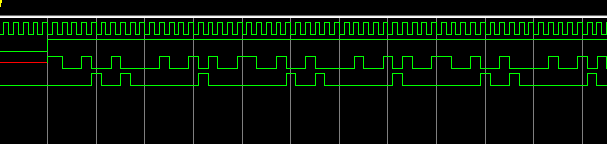

模块功能:对串行输入的数据流进行检测。只要发现10010序列,就立即输出高电平。

*************************************************************************/

module seqdet(x,z,clk,rst_n);

input clk,rst_n;

input x;

output z;

reg z;

reg [2:0] pstate,nstate;

parameter s1=3'd0,

s2=3'd1,

s3=3'd2,

s4=3'd3,

s5=3'd4,

s6=3'd5;

//* 使用热独码会更好些。

//第一段: 现态与次态转换 时序电路

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

pstate<=s1;

else

pstate<=nstate;

end

//第二段:各种状态间的跳变。 组合电路

always @(pstate or x)

begin

case(pstate)

s1:

if(x==1)

nstate=s2;

else

nstate=s1;

s2:

nstate=x?s2:s3;

s3:

nstate=x?s2:s4;

s4:

nstate=x?s5:s1;

s5:

nstate=x?s2:s6;

s6:

nstate=x?s2:s4;

default:

nstate=s1;

endcase

end

//第三段:确定最终的状态

always @(pstate or x or rst_n)

begin

if(!rst_n==1)

z=1'b0;

else if(pstate==s5 && x==0)

z=1'b1;

else

z=1'b0;

end

endmodule

```

```

`timescale 1 ns/ 1 ps

module seqdet_vlg_tst();

reg clk;

reg rst_n;

wire x;

wire z;

reg[19:0] data;

assign x=data[19];

seqdet i1 (

.clk(clk),

.rst_n(rst_n),

.x(x),

.z(z)

);

initial

begin

clk=0;

rst_n=0;

#500 rst_n=1;

data=20'b1100_1001_0000_1001_0100;

#(100*100) $stop;

end

always

#50 clk=~clk;

always @(posedge clk)

begin

#2 data={data[18:0],data[19]};

end

endmodule

```

- 空白目录

- 流水线

- 流水线性能测评

- 计算机性能测评

- 流水线设计

- 购物车状态机

- 序列检测器

- 序列检测10010

- 序列检测10010带图

- 反相器

- 计数器

- 分频电路

- 偶数分频

- 奇数分频

- 小数分频

- 同步复位异步释放all

- 对的-异步复位同步释放原理

- 同步复位异步释放

- 异步复位为什么要同步释放 ?

- FPGA-异步复位同步释放 通俗解释

- 同步复位

- 状态机

- 状态机的分类

- 状态机5个要素

- FIFO

- 异步fifo中同步为什么要用两级触发器

- 亚稳态

- 亚稳态的产生机理、消除办法 (可以理解为什么打拍)

- 面向对象思想

- 为什么D触发器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自启动

- 毛刺

- 冯诺依曼