时钟分频电路(分频器)在IC设计中经常会用到,其目的是产生不同频率的时钟,满足系统的需要。比如一个系统,常规操作都是在1GHz时钟下完成,突然要执行一个操作涉及到模拟电路,所需时间是us量级的,显然用1GHz(周期是1ns)的时钟进行操作是不合适的。

时钟分频器电路可以分为数字分频器、模拟分频器和射频分频器等。数字分频器通过一个计数器来进行分频,权值为分频系数。模拟分频器就是一个频率分配器,用带阻带通实现。射频分频器也是滤波器原理,用带内外衰减,阻抗匹配实现。

对于精度不高的场合,数字分频器分出的时钟就可以满足要求。常用到数字分频器有2,4,6,8,……偶数分频,也会有3,5,7,9……奇数分频,甚至还会有8.7,11.2,6.432,……分数分频。

偶数分频是最容易掌握的,奇数分频就有些技巧,如果你不知道奇数分频技巧,就可能会被一些公司的面试或者考试题目给难住,错失一些机会。而像8.7,11.2,6.432,……这种分数分频器就更需要技巧。掌握这些通用的技巧就能很快的实现各种分频器,满足系统的需求。下面IC君就跟大家分别聊一下偶数分频、奇数分频、分数(小数)分频器。

**偶数分频**

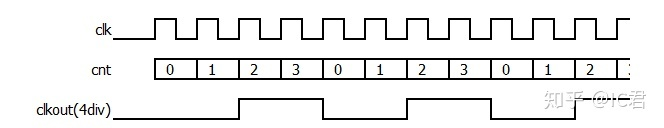

偶数分频器的实现简单,用计数器在上升沿或者下降沿计数,当计数器的值等于分频系数的一半或等于分频系数时,信号翻转。偶数分频器分频原理如下图所示:

上图的的分频系数是4,就是4分频。电路原理是用一个上升沿计数的计数器,每次计数到2时输出信号clkout翻转一次,每次计数到4时clkout再翻转一次,一直周期重复下去。其他的偶数分频器原理也是一样。从波形中可以看出cnt 从00->01->10->11->00...... 一直循环记数,如果你够仔细,就可以看出cnt的最高位其实也是一个4分频的时钟。

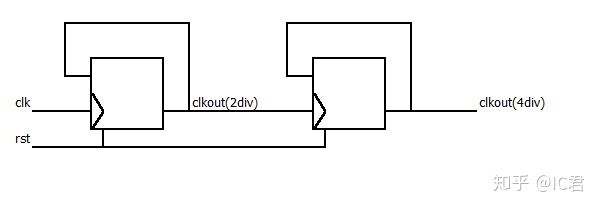

如果偶数分频系数是2的幂,就可以用2分频器级联得到;例如4分频就是两个2分频级联,下图就是用两个2分频器级联得到4分频器。

- 空白目录

- 流水线

- 流水线性能测评

- 计算机性能测评

- 流水线设计

- 购物车状态机

- 序列检测器

- 序列检测10010

- 序列检测10010带图

- 反相器

- 计数器

- 分频电路

- 偶数分频

- 奇数分频

- 小数分频

- 同步复位异步释放all

- 对的-异步复位同步释放原理

- 同步复位异步释放

- 异步复位为什么要同步释放 ?

- FPGA-异步复位同步释放 通俗解释

- 同步复位

- 状态机

- 状态机的分类

- 状态机5个要素

- FIFO

- 异步fifo中同步为什么要用两级触发器

- 亚稳态

- 亚稳态的产生机理、消除办法 (可以理解为什么打拍)

- 面向对象思想

- 为什么D触发器有setup time和hold time的要求

- Tsu,Tco,Th,Tpd的概念

- verilog

- 自启动

- 毛刺

- 冯诺依曼