在同一时刻,我们只需保证对某个内存地址的操作是原子性即可,但总线锁定把CPU和内存之间的通信锁住了,这使得锁定期间,其他处理器不能操作其他内存地址的数据,所以总线锁定的开销比较大,目前处理器在某些场合下使用缓存锁定代替总线锁定来进行优化。

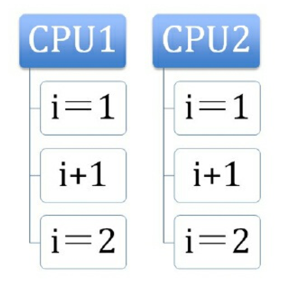

频繁使用的内存会缓存在处理器的L1、L2和L3高速缓存里,那么原子操作就可以直接在处理器内部缓存中进行,并不需要声明总线锁,在Pentium6和目前的处理器中可以使用“缓存锁定”的方式来实现复杂的原子性。_**所谓“缓存锁定”是指内存区域如果被缓存在处理器的缓存行中,并且在Lock操作期间被锁定,那么当它执行锁操作回写到内存时,处理器不在总线上声言LOCK#信号,而是修改内部的内存地址,并允许它的缓存一致性机制来保证操作的原子性,因为缓存一致性机制会阻止同时修改由两个以上处理器缓存的内存区域数据,当其他处理器回写已被锁定的缓存行的数据时,会使缓存行无效**_,在如下图所示的例子中,当CPU1修改缓存行中的i时使用了缓存锁定,那么CPU2就不能同时缓存i的缓存行

#### 但是有两种情况下处理器不会使用缓存锁定

第一种情况是:当操作的数据不能被缓存在处理器内部,或操作的数据跨多个缓存行(cacheline)时,则处理器会调用总线锁定。

第二种情况是:有些处理器不支持缓存锁定。对于Intel486和Pentium处理器,就算锁定的内存区域在处理器的缓存行中也会调用总线锁定。

针对以上两个机制,我们通过Intel处理器提供了很多Lock前缀的指令来实现。例如,位测试和修改指令:BTS、BTR、BTC;交换指令XADD、CMPXCHG,以及其他一些操作数和逻辑指令(如ADD、OR)等,被这些指令操作的内存区域就会加锁,导致其他处理器不能同时访问它

- 简介

- 概述

- 进程vs线程

- 资源限制

- 有关并行的两个定律

- 线程同步和阻塞

- 线程阻塞

- 线程的特性

- 守护线程

- 线程异常

- Thread

- 线程状态

- 线程中断

- wait¬ify

- suspend&resume

- join&yield

- notify¬ifyAll

- Thread.sleep

- 线程任务

- Runnable

- Callable

- Future模式

- FutureTask

- 线程实现方式

- 内核线程实现

- 用户线程实现

- 混合实现

- Java线程的实现

- java与协程

- 纤程-Fiber

- 线程调度

- 多线程协作方式

- 阻塞

- 放弃

- 休眠

- 连接线程

- 线程估算公式

- 线程活跃性

- 死锁

- 线程安全性

- 对象的发布与逸出

- 构造方法溢出

- 线程封闭

- 对象的可变性

- 原子性

- 原子操作

- CPU原子操作原理

- 总线锁

- 缓存锁

- JAVA如何实现原子操作

- long和double读写操作原子性

- Adder和Accumulator

- 线程性能

- 同步工具类

- 闭锁

- CountDownLatch

- FutureTask

- 信号量

- 栅栏

- CyclicBarrier

- Exchanger

- 并发编程

- volatile

- synchronized

- 无锁

- 偏向锁

- 轻量级锁

- 锁的优缺点对比

- 锁升级

- 锁消除

- Monitor

- synchronized语法

- Mutex Lock

- synchronized实践问题

- synchronized&ReentrantLock

- Lock

- ReentrantLock

- Condition

- 读写锁

- ReadWriteLock

- StampedLock

- 线程池

- Executor

- ExecutorService

- Executors

- ThreadPoolExecutor

- RejectedExecutionHandler

- ThreadFactory

- 线程池大小公式

- 动态调整线程池大小

- Fork/Join框架

- ForkJoinPool

- CompletableFuture

- JUC并发工具包

- LockSupport

- 延时任务与周期任务

- Timer

- TimerTask

- 异构任务并行化

- CompletionService

- volatile和synchronized比较

- 锁优化

- 锁相关概念

- 悲观锁(排它锁)

- 乐观锁

- 自旋锁

- 乐观锁vs悲观锁

- JVM锁优化-锁消除

- ThreadLocal

- InheritableThreadLocal

- TransmittableThreadLocal

- ThreadLocalRandom

- 无锁

- AtomicInteger

- Unsafe

- AtomicReference

- AtomicStampedReference

- AtomicIntegerArray

- AtomicIntegerFieldUpdater

- 无锁Vector

- LongAdder

- LongAccumulator

- 常见锁类型

- 悲观锁&独占锁

- 乐观锁

- 乐观锁vs悲观锁

- 自旋锁vs适应性自旋锁

- 公平锁vs非公平锁

- 可重入锁vs非可重入锁

- 独享锁vs共享锁

- 互斥锁

- CAS

- AQS介绍

- AQS深入剖析

- AQS框架

- AQS核心思想

- AQS数据结构

- 同步状态State

- ReentrantLock vs AQS

- AQS与ReentrantLock的关联

- ReentrantLock具体实现

- 线程加入等待队列

- 等待队列中线程出队列时机

- 如何解锁

- 中断恢复后的执行流程

- ReentrantLock的可重入应用

- JUC中的应用场景

- 自定义同步工具

- CLH锁

- 并发框架

- Akka

- Disruptor-无锁缓存框架

- 常见面试题

- 两个线程交替打印A和B

- 附录