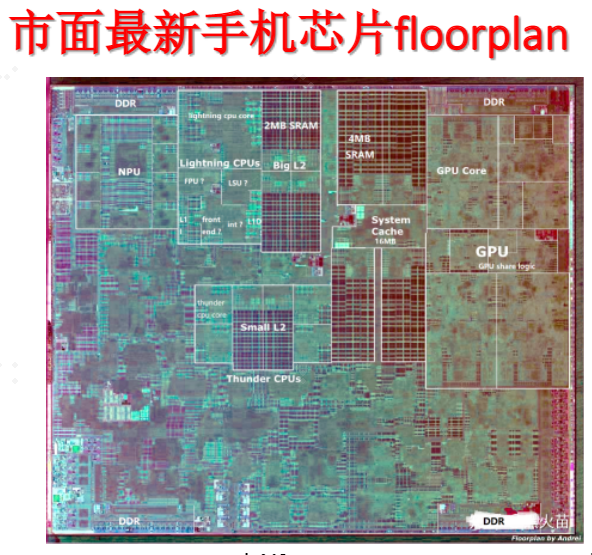

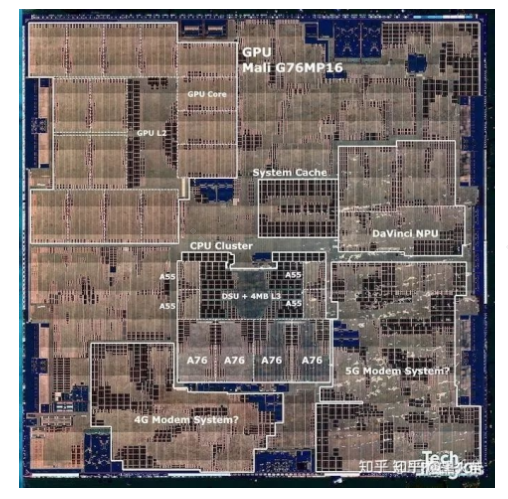

Floorplan的目的是为了确定模块大小,位置,形状,以及摆放Macro,也就是我们通常见到的随机存储单元RAM、只读存储单元ROM,还有其他IP模块等等。它与Place(布局)有着一些相似的地方。Floorplan的复杂之处在于模块的形状与大小可能是一个不确定的变量,需要权衡结果来反推这个变量。而其简单之处在于,Floorplan相比于Place的超大规模标准单元而言,整体数据量并不是十分庞大。

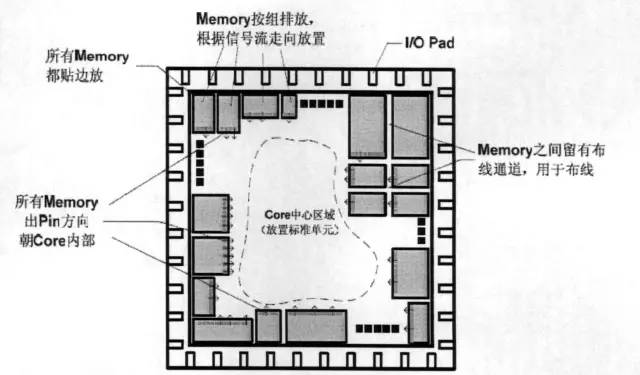

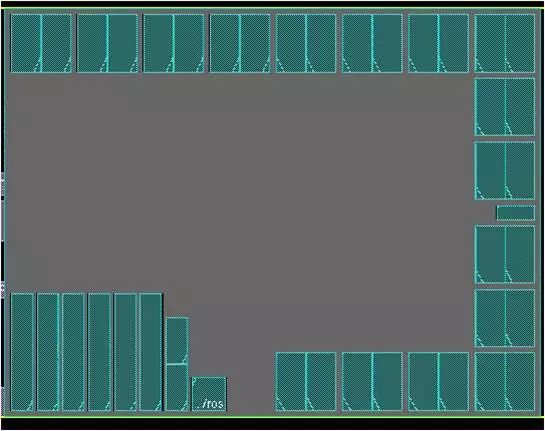

对于Floorplan而言,人们更倾向于靠自己的经验去摆放Macro,摆放它们时不仅要考虑面积、互联线长等传统问题,还需要考虑Place阶段,Macro的摆放对于Place的影响。因为Macro从本质上讲就是一个巨型的标准单元,很多Macro也存在于各个模块内,在Floorplan阶段并不能和模块对等的考虑。对于这个问题,人们根据实际生活中的经验,提出一种边缘摆放(edgeplace)的方法

因为长久以来,人们在使用具有矩形或者多边形结构的平面石砖砌墙或者铺地面的时候发现一个规律,要想更好的利用手头的材料,更少的产生材料的冗余,需要先从平铺区域的边边角角开始工作,并且首先将最大块的材料铺于区域中,再向中心扩展,并用一些小材料填补区域上的空隙。

边缘摆放的好处主要来源于下面两点:

a.从目前芯片设计的趋势来看,芯片中除了计算单元,随机存储单元RAM、只读存储单元ROM等。这些存储单元占据的芯片面积在有些设计中甚至超过百分之五十。对于存储单元来说,存在数据端口和存储端口,并且周围需要有一些可测性[电路]。这使得这些单元引线众多且功耗巨大。将它们贴边放置,不仅有利于这些单元的供电,而且防止这些单元过多的引脚对其他单元的布线造成影响。

b.标准单元在布局时,按照Row所划定的高度一排一排的摆放,这样既有利于算法的设计,又有利于工业制造。并且在给各个器件供电时,可以使用横向的电源线将处于同一高度的器件连接在一起统一供电。若是将标准单元都摆放在芯片区域的中心,而大的Macro摆放在四周,就可以使标准单元方便的只用一条电源线连接在一起,而不会被高度不统一的Macro打断。对电源网格的设计提供了巨大便利。

b.大的Macro摆放尽量贴近版图的边缘和角落,这样有利用空间的利用。如下图所示

c.Macro与Macro之间要留有一定空隙,给予布线资源。特别是在Macro的间隙有端口的时候更是如此,设计者可以通过相邻Marco边界上端口的多少来决定留有多大的间隙比较合适。在使用[EDA](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)软件的Floorplan设计时,同样可以给Macro加上halo来控制Macro与Macro之间的距离。Halo分为placementhalo和rou[ti](http://www.elecfans.com/tags/ti/)nghalo,可以分别阻止在有Halo区域放置其他单元或者绕线,类似于blockage。但是Halo并不是独立存在,而是依附于Macro周围,可随Macro移动的。所以它是专门用来控制Macro和其他单元之间距离的一种功能。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning