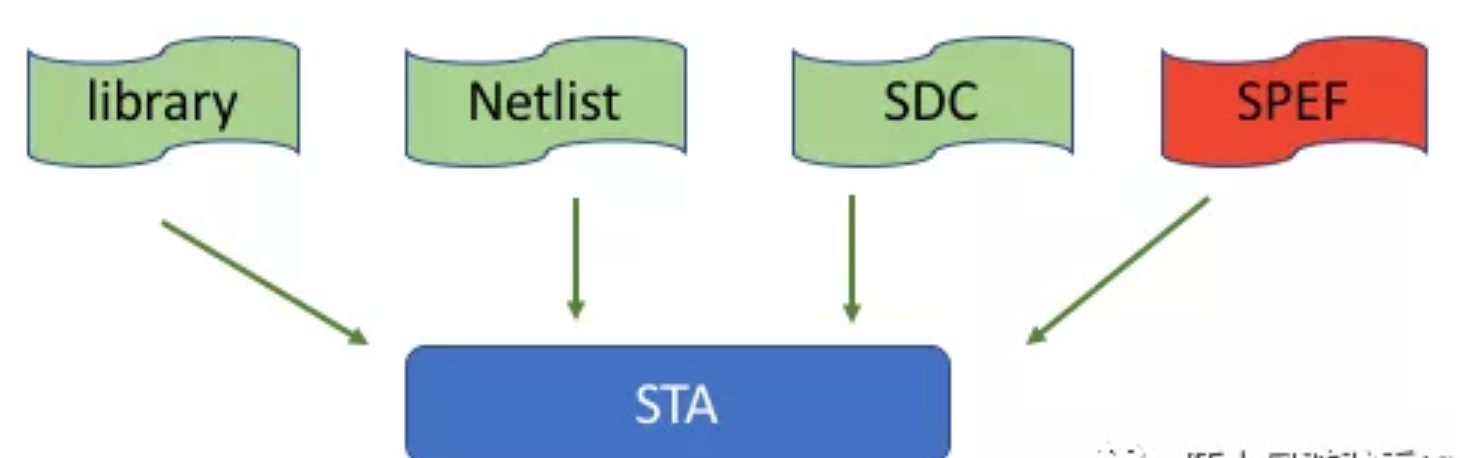

RC corner,这里的RC指gate跟network的寄生参数,寄生参数抽取工具根据电路的物理信息,抽取出电路的电阻电容值,再以寄生参数文件输入给STA工具,常见的寄生参数文件格式为SPEF。

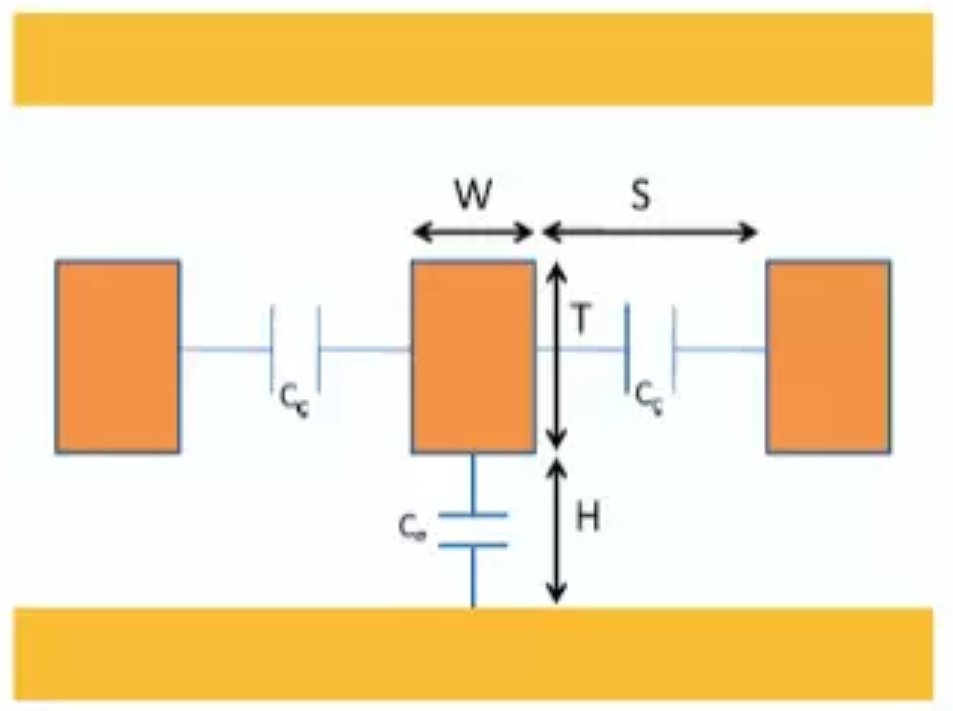

ICer都知道在集成电路中是多层走线的,专业术语叫metal layer,不同工艺有不同层metal layer,任何两层metal layer间由介电材料隔离,『走线』通过过孔(VIA)连接。Width跟Spacing是衡量绕线的两条最重要的物理设计规则,它们随着工艺的进步逐步减小。 介电材料、绕线材料、线间距、线宽及线的厚度这些物理特性决定了network的RC值。

**Network电容:**

* 耦合电容:Coupling capacitance=e\*T/S

* 表面电容:Surface capcitance=e\*W/H

* 边缘电容:Fringe capcitance

**决定容值的因素:**

* 介电常数:e

* 线宽:W

* 线厚:T

* 线间距:S

* 介电材料的厚度:H

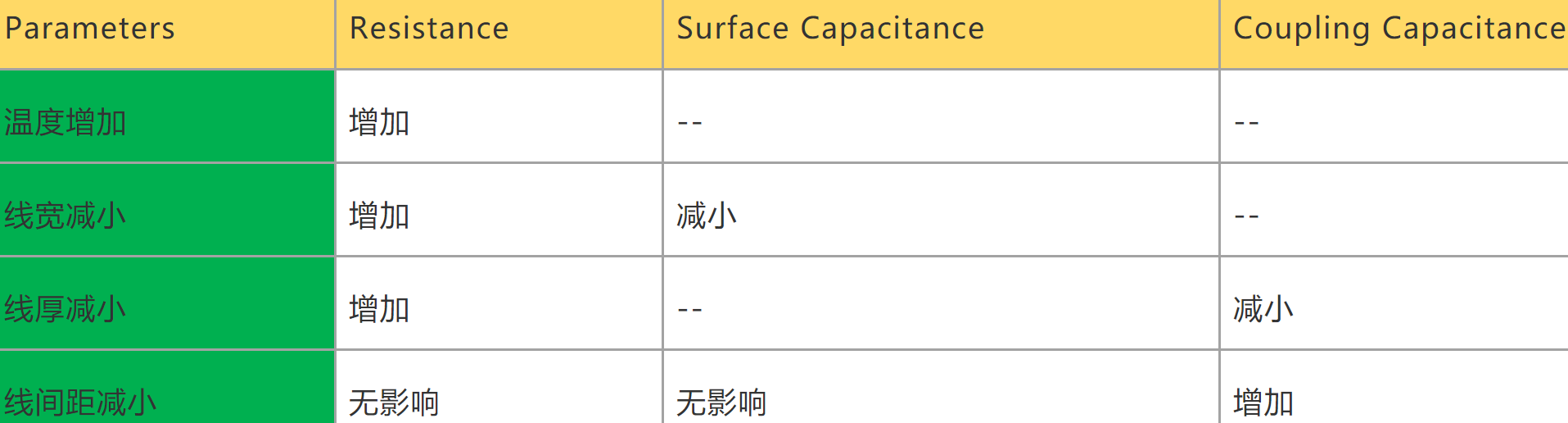

随着工艺进步,W, S, T 逐代递减,表面电容跟随减小,耦合电容随之增加,耦合电容在总电容中占比增加,当线厚 T 一定时为了减少耦合电容要么增加线间距要么减小介电常数。通常为了减小噪声敏感信号线(如clock net)上的耦合电容,在物理实现时会人为增加对应信号的线宽及线间距,俗称NDR。要减小介电常数需要从材料入手,从 .18开始引入low K介电材料。

**Network电阻:**

R=r/W\*T, r为电阻率,除了跟线宽 W 和线厚 T 相关之外,还跟温度相关,随着温度的上升而增大。

由上面的分析可知,Network的单位电容和单位电阻是不可能同时最大或同时最小的。有了这些铺垫,来看一下不同工艺结点是如何定义RC corner的。

90nm 之前,Cell delay占主导,Network电容主要是对地电容,STA只需要两个RC corner即可:

* Cbest(Cmin): 电容最小电阻最大

* Cworst(Cmax):电容最大电阻最小

90nm 之后,netdelay的比重越来越大,而且network的耦合电容不可忽略,所以又增加了两个RC corner:

* RCbest(XTALK corner): 耦合电容最大,(对地电容\*电阻)最小

* RCworst(Delay corner): 耦合电容最小,(对地电容\*电阻)最大

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning