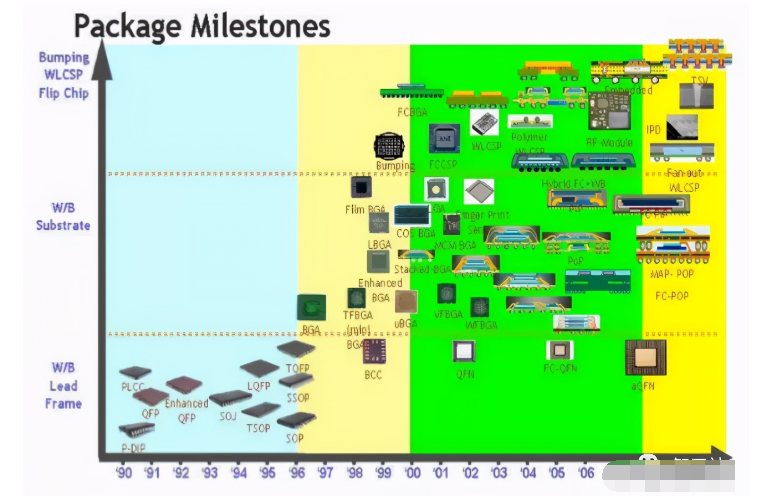

随着现代电子装置对小型化、轻量化、高性能化、多功能化、低功耗化和低成本化方面的要求不断提高,IC芯片的特征尺寸不断缩小,且集成规模迅速扩大,芯片封装技术也在不断革新,凸点加工工艺(Bumpprocessflow)也因此发展起来。

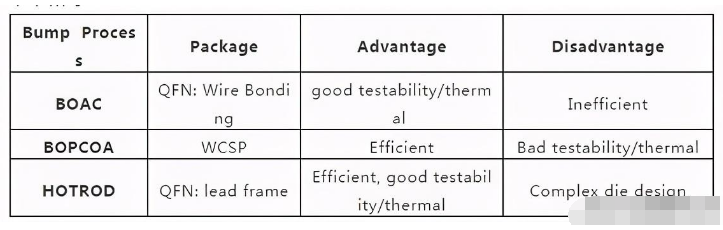

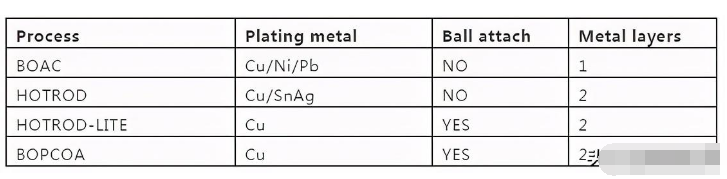

Bumpprocess分为三种:BOPCOA、BOAC、HOTROD,其封装的优缺点如下表所示。

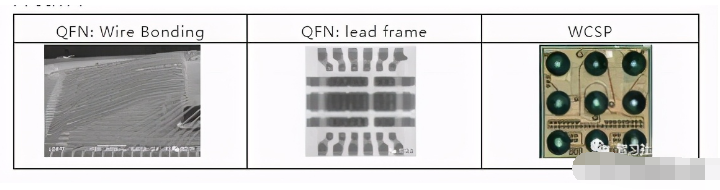

对于芯片尺寸要求没那么严格的情况,大多数产品都是采用QFN封装形式的芯片,因其可测性和散热较好;而对于耳机、手机等小型化产品的芯片,大多采用WSCP(wafers calechippackage)封装。同一种功能的芯片而言可以加工成不同的封装形式,仅在Bump和Assembly层面有所区别,可以理解为QFN封装在完成Bump制程后还需要打线(WireBonding)或者引线框架(leadframe)将引脚引出,最后塑封[成型](http://www.hqpcb.com/),而WCSP则在Bump完成Ballattach之后就是一颗完整可以交付到客户手上的芯片了,这可以减少很多的设计开发成本。

为了更好的理解bump制程工艺,接下来简单介绍一下WCSP的工艺流程。

Bump的制程在fab之后,fab是将电路部分加工完成,一般有三层metal,最上层留有[via](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)top,便于bump进行下一步的加工。一般从fab过来的wafer都会有一道宏观检测,去检测是否从fab过来就有defect,类似[刮伤](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)、[污染](http://www.hqpcb.com/zhuoluye11/?tid=26&plan=fashaoyou)、破片之类的问题。然后再做清除和烘烤去除wafer上的松散颗粒和有机污染物以及wafer上的水分。

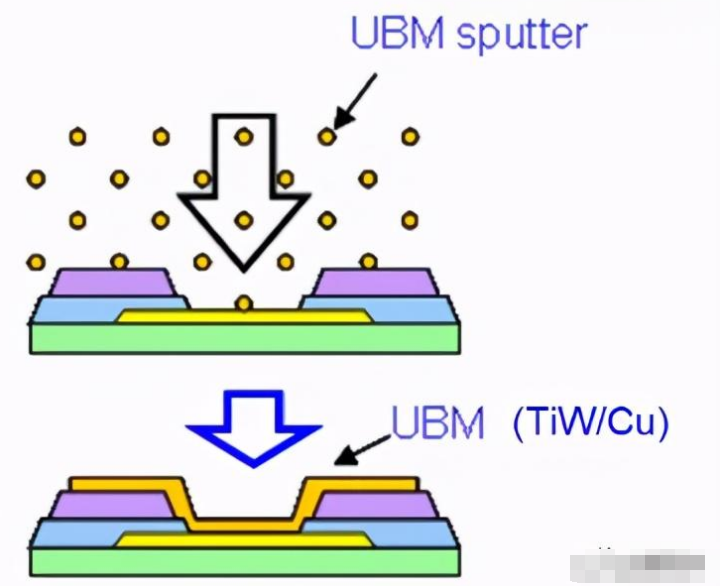

完成了前序动作,才真正开始bump制程,首先在incoming的wafer上溅镀上一层薄薄的金属层,一般是3um-[Ti](http://www.elecfans.com/tags/%E5%BE%B7%E5%B7%9E%E4%BB%AA%E5%99%A8/)w和2um-Cu,为fab的电路提供保护层并为fab和bump之间创建金属互连层。

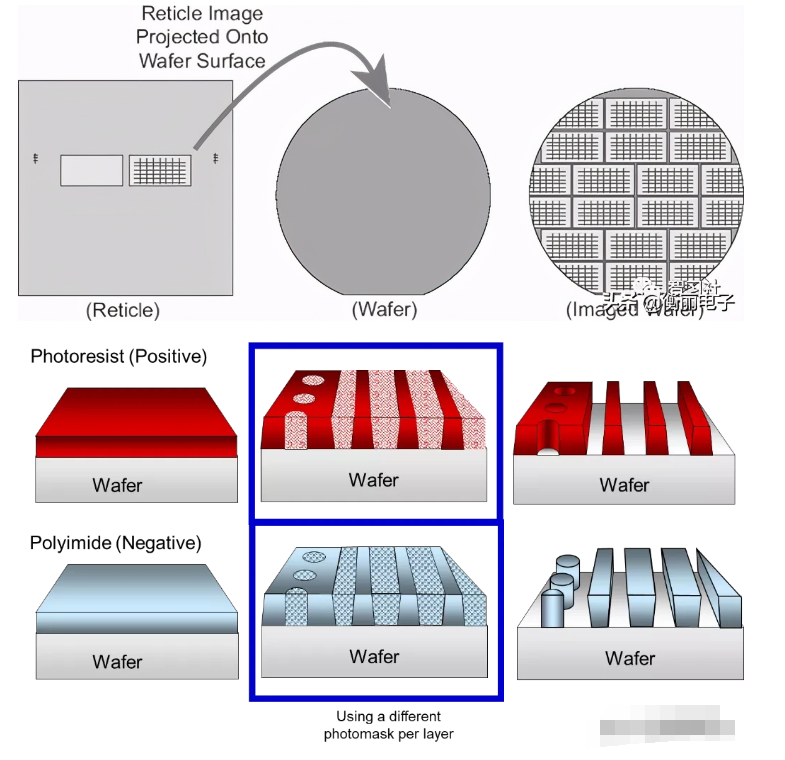

溅镀完一层金属薄膜之后整片wafer都是导电的,不能直接进行[电镀](http://www.hqpcb.com/),需要先铺光阻做图案,只露出需要电镀的区域并将不需要电镀的地方保护起来,这个过程称为photo制程。Photo制程分为铺光阻、曝光、显影,先将整片wafer铺上光阻(光阻分为正性光阻和负性光阻,其区别在于被光照过的地方是易溶解还是不易溶解),然后利用带有所需图形的光照板进行曝光后得到所需的图形,曝光所用的机台就是我们常听到的光刻机,不同机台的功能一样,只是原理有所不同,光刻机的精度直接影响芯片的尺寸大小以及一定尺寸下芯片电路的复杂程度。光阻经过曝光,会使得有些地方易于被显影液溶解,有些地方则不易被溶解,因此经过显影之后需要电镀的地方就会被裸露出来。

光阻铺完接下来则是电镀,常用的电镀方法有挂镀法和垂直镀法,目前采用的大多是垂直镀法,电镀的原理简单来说就是铜离子失去电子得到铜并在电场的作用下沉积在wafer表面,根据给定的[电流](http://www.elecfans.com/tags/%E7%94%B5%E6%B5%81/)密度和电镀时间控制电镀铜的高度。BOAC是电镀CU+Ni+Pb,也只电镀一层金属,而HOTROD和BOPCOA这一层metal为重分布层(COA/RDL),还需重复一次sput[te](http://www.elecfans.com/tags/te/)r+photo+plating制程,另外通常在两层金属之间会加一层polyimide进行防护。常规HOTROD制程的SnAg是直接通过电镀完成然后进行reflow,而HOTROD-LITE和BOPCOA在电镀过程中只镀Cu,SnAg是通过ballattach+reflow完成的。

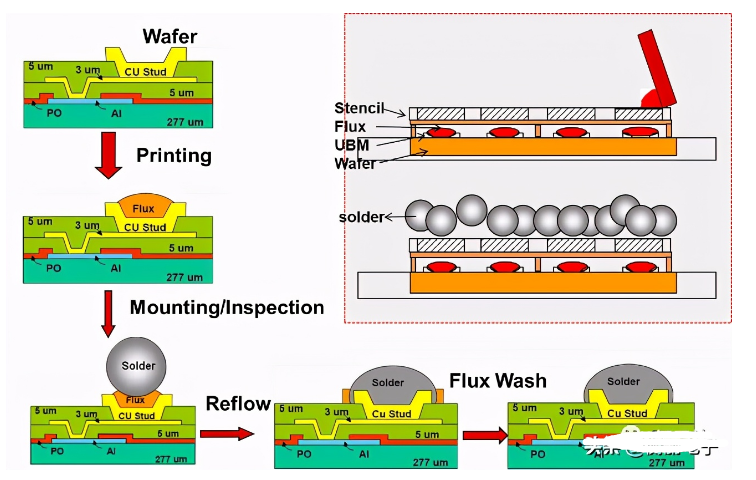

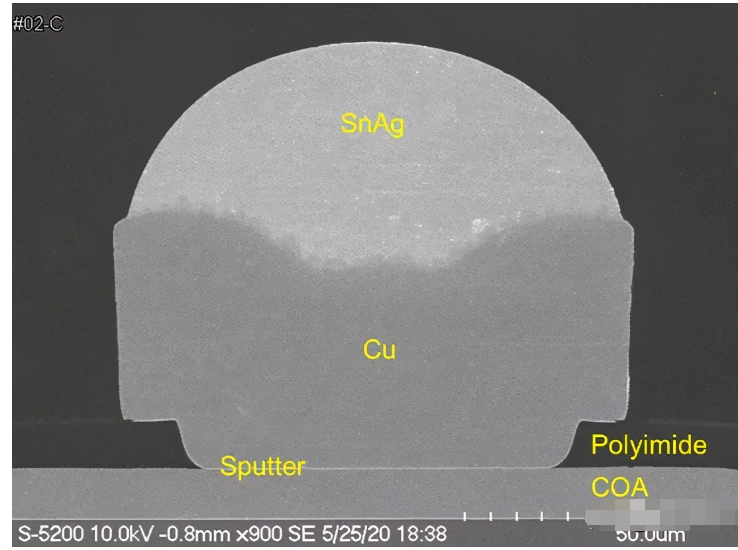

下图为BOPCOA制程进行Ballattach的详细过程:先在wafer表面涂上助焊剂,然后将锡银球通过stencil置于对应的UBM上,然后经过reflow完成solder的植球过程。下图给出为实际的bump结构的SEM-cut图。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning