https://blog.csdn.net/zyn1347806/article/details/111804012

1.什么是SPEF

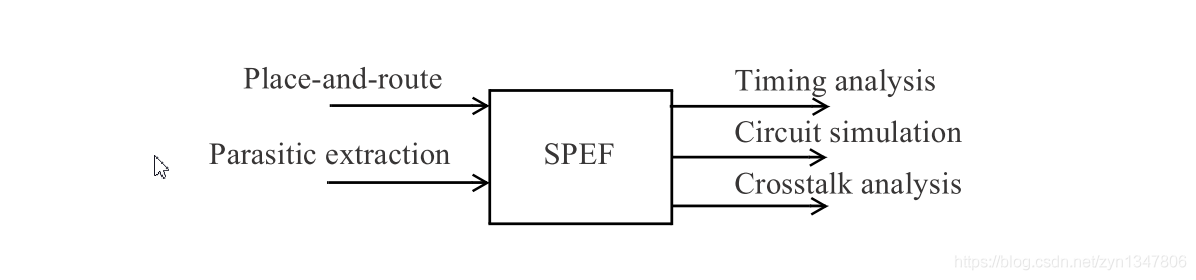

SPEF是Standard Parasitic Extraction Format的缩写,用于描述芯片在PR之后实际电路中的 R L C 的值。由于芯片的 current loops非常窄也比较短,所以一般不考虑芯片的电感,所以通常SPEF中包含的寄生参数为RC值。SPEF被后端StarRC工具抽取并用于之后的STA。

## 2.SPEF的模型

SPEF支持以下三种net模型

* distribute net model

* reduced net model

* lumpped capacitance model

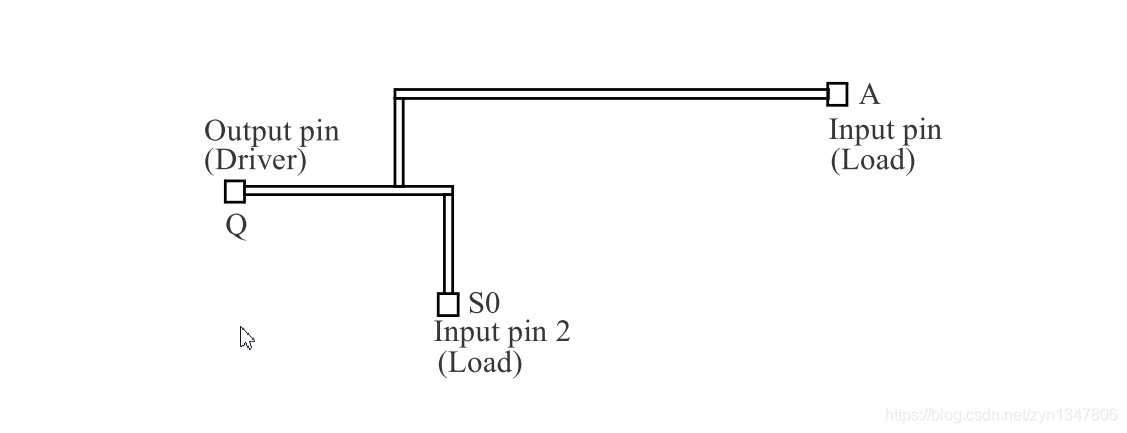

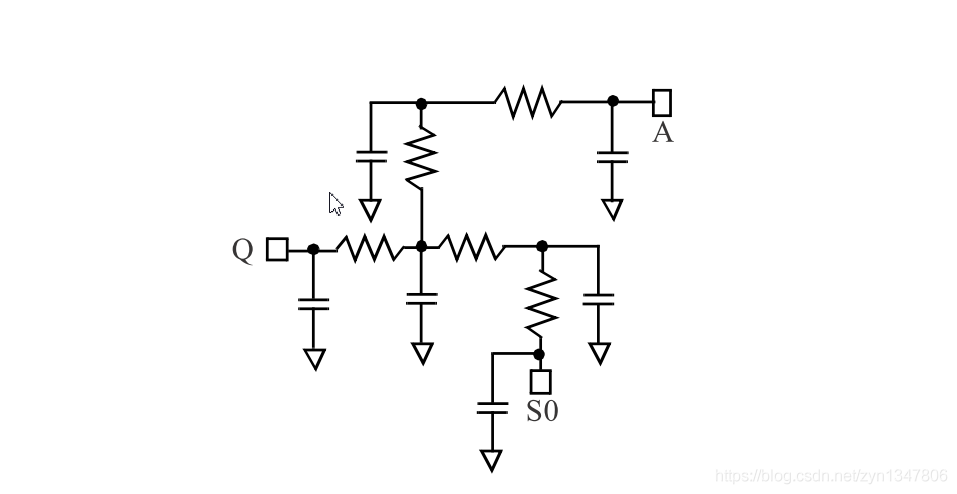

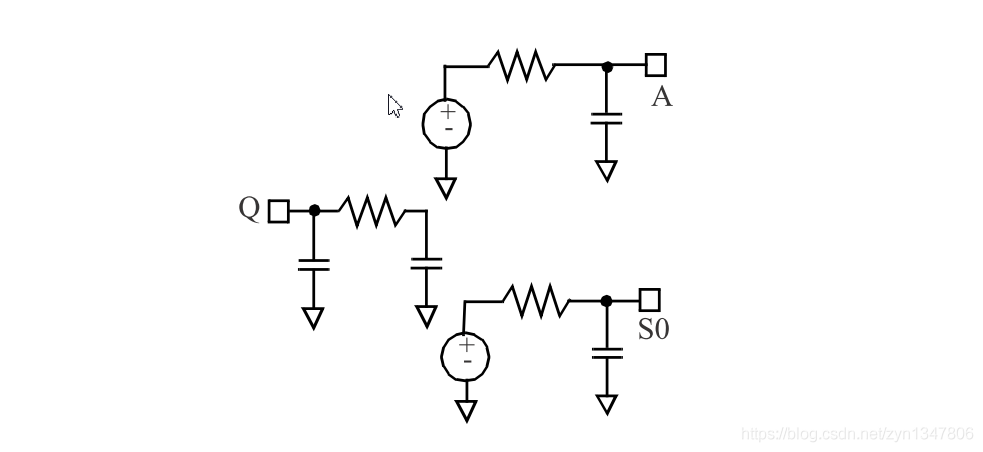

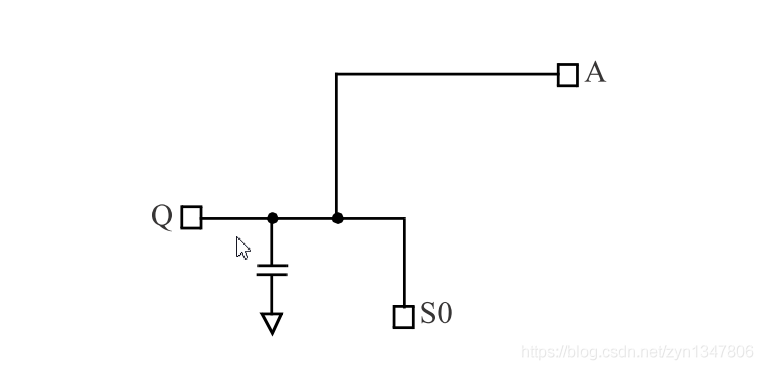

例如,对于下图的连接线

三种模型分别抽象为

distribute net[model](https://so.csdn.net/so/search?q=model&spm=1001.2101.3001.7020)每一段net都有自己独立的RC值

reduced net model Load pin是一个简化的RC值,driven 拼端将RC模型简化为一个pie model

lumpped capacitance model 将所有net的cap简化为一个单一的cap值

3 SPEF文件的内容

SPEF文件的总体格式如下。下面分别介绍这几部分的含义。

```

header_definition

[ name_map ]

[ power_definition ]

[ external_definition ]

[ define_definition ]

internal_definition

```

## 3.1 header\_definition

一个典型的head definition如下所示,内容 基本上看一下就明白这里不过多介绍

~~~swift

*SPEF "IEEE 1481-1998"

*DESIGN "ddrphy"

*DATE "Thu Oct 21 00:49:32 2004"

*VENDOR "SGP Design Automation"

*PROGRAM "Galaxy-RCXT"

*VERSION "V2000.06 "

*DESIGN_FLOW "PIN_CAP NONE" "NAME_SCOPE

LOCAL"

*DIVIDER /

*DELIMITER :

*BUS_DELIMITER [ ]

*T_UNIT 1.00000 NS

*C_UNIT 1.00000 FF

*R_UNIT 1.00000 OHM

*L_UNIT 1.00000 HENRY

// A comment starts with the two characters “//”.

// TCAD_GRD_FILE /cad/13lv/galaxy-rcxt/

t013s6ml_fsg.nxtgrd

// TCAD_TIME_STAMP Tue May 14 22:19:36 2002

~~~

## 3.2 name map

```

*NAME_MAP

*1 memclk

*2 memclk_2x

*3 reset_

*4 refresh

*5 resync

*6 int_d_out[63]

*7 int_d_out[62]

*8 int_d_out[61]

*9 int_d_out[60]

*10 int_d_out[59]

*11 int_d_out[58]

*12 int_d_out[57]

. . .

*364 mcdll_write_data/write19/d_out_2x_reg_19

*366 mcdll_write_data/write20/d_out_2x_reg_20

*368 mcdll_write_data/write21/d_out_2x_reg_21

. . .

*5423 mcdll_read_data/read21/capture_data[53]

. . .

*5426 mcdll_read_data/read21/capture_pos_0[21]

. . .

*11172 Tie_VSSQ_assign_buf_318_N_1

. . .

*14954 test_se_15_S0

*14955 wr_sdly_course_enc[0]_L0

*14956 wr_sdly_course_enc[0]_L0_1

*14957 wr_sdly_course_enc[0]_S0

```

## 3.3 power definition

该部分定义了power的相关内容

~~~markdown

*POWER_NETS VDDQ

*GROUND_NETS VSSQ

~~~

## 3.4 external definition

定义了设计中的逻辑和物理的关系。例如,对于port的逻辑定义格式如下

```

*PORTS

port_name direction { conn_attribute }

port_name direction { conn_attribute }

. . .

```

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning