上面列举了芯片设计领域比较常见的低功耗设计方向,其中应用最多的就是优化芯片架构,升级生产工艺、降低芯片工作电压、采用不同速度的标准单元,分区域采用不同电压的电源以及模块关断(多电压域),而其中和后端设计有关的,基本上有以下几种:

**升级生产工艺;**

**降低芯片工作电压;**

**关断部分时钟(Clock Gating);**

**采用不同速度的标准单元(Multi-Vth库);**

**多电压域设计(Multi-Voltage)。**

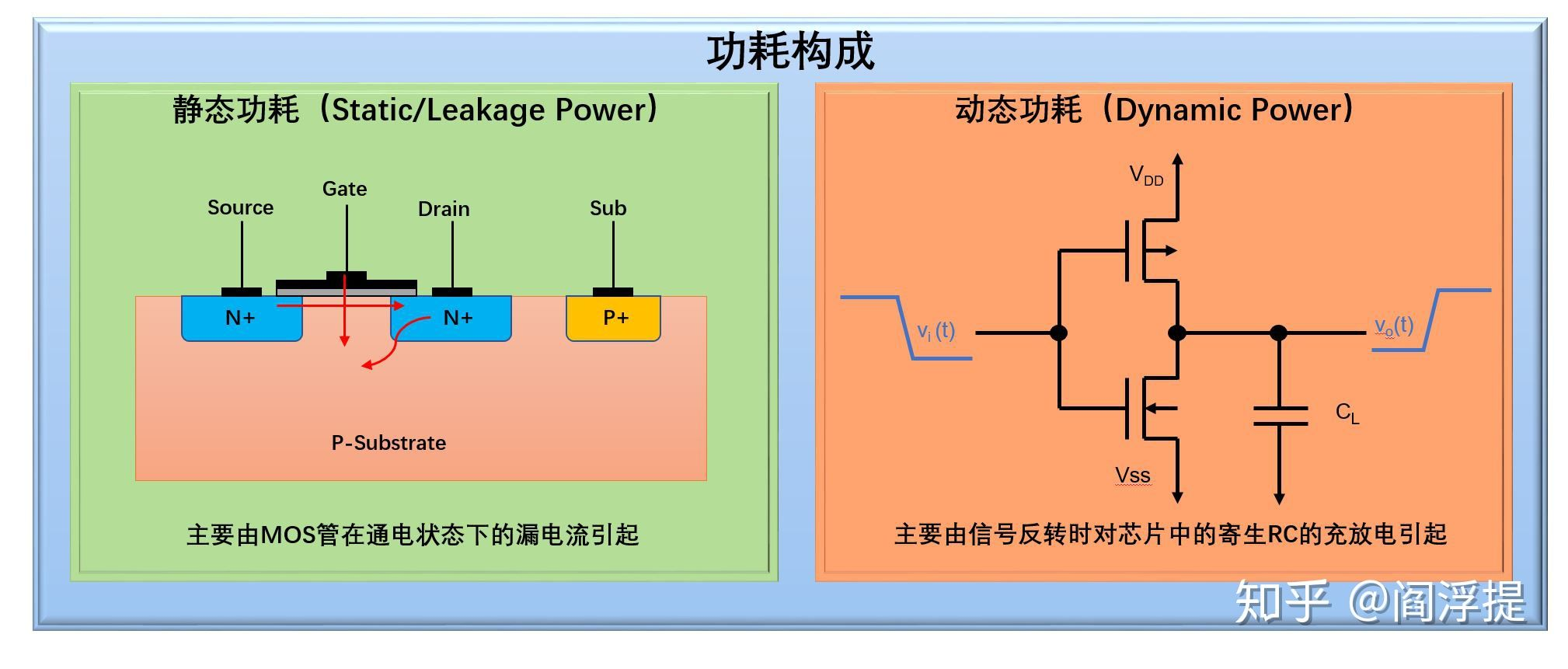

在详细解释上述概念之前,我想先把芯片中主要的功耗构成简单提一下。芯片功耗主要分为静态功耗和动态功耗,基本原理如下图所示:

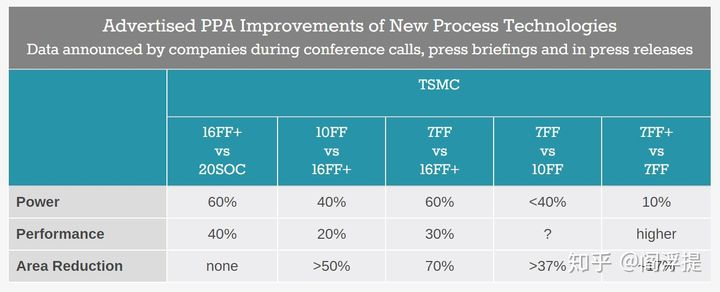

* **升级工艺**

这是应用最广泛,最行之有效的方法之一。它的原理在于,随着晶体管的尺寸越来越小,leakage power在芯片整体功耗中所占的比重越来越大,而先进工艺的晶体管尺寸更小,泄漏电流也更小,从而能够整体降低leakage power。因此我们经常能够看到这样的新闻:某某芯片从22nm升级到14nm,性能提升x%,功耗降低y%等。这其中的功耗降低固然可能包含架构方面的改善,但是工艺升级带来的优势一定是非常明显的。

* **降低芯片工作电压**

按照中学物理的计算公式,功率与电压和电流的乘积正相关。在芯片上计算功耗虽然没有这么简单,但是从原理上降低芯片电压仍然是降低功耗最直观最有效的方法。也正因为如此,当前大多数芯片的工作电压从最初的5V、3V一路下降,目前基本都在1V以下甚至0.5V以下。而随之而来的困难在于,随着电压的下降,标准单元的速度也会随之变慢,但是电子设备对处理速度亦即芯片频率的要求却越来越高。以移动设备为例,最初的芯片频率不过几十上百兆赫兹,而现今最快的手机SoC频率峰值已经超过2GHz。这方面也是每一代芯片升级背后所需要解决的技术难题之一。

* **关断时钟(Clock Gating)**

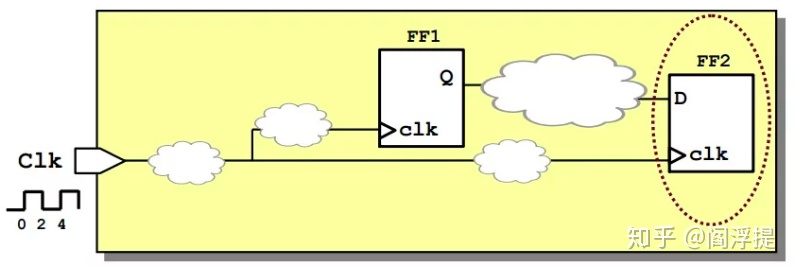

动态功耗主要是由信号的翻转引起的,而在芯片中,翻转最频繁的信号就是时钟(Clock)信号。我们知道,芯片中各种逻辑功能的传输,数据保存等电路是由下列timing path组成的:

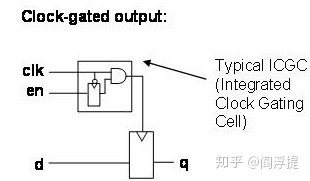

简而言之,就是前面的FF1寄存器的数据通过一系列运算后,在时钟信号clk的作用下,被后面的FF2寄存器捕捉,完成一次数据传输。但在实际中会有这样的情况发生:FF1传过来的数据和FF2当前保存的数据相同,也就是FF2的数据无需翻转刷新仍能保证功能的正确性,而此时clk仍然翻转一次刷新了FF2的数据。这种情况尽管在功能上没有任何问题,但是在功耗方面却是实实在在的浪费。因此,在电路设计阶段以及逻辑综合阶段,设计者和EDA工具会根据芯片的功能和实际数据的变化情况,人为或者自动地插入一系列的clock gating cell,从而保证仅在数据发生变化的时候信号才会翻转。下面是典型的Integrated Clock Gating(ICG)的结构:

* **采用不同速度的标准单元(Multi-Vth库)**

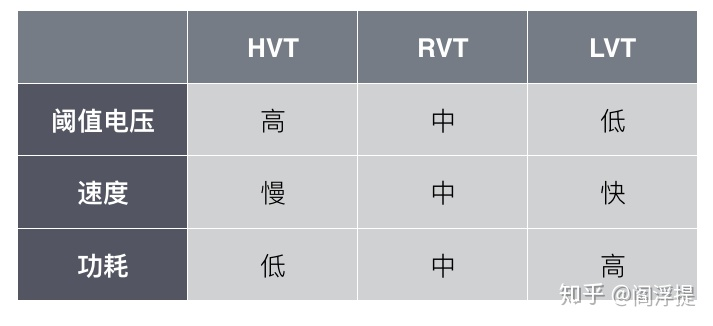

这是当前芯片行业最常用也是最容易使用的设计方法之一。所谓Vth,指的是逻辑门的阈值电压。而阈值电压和功耗与速度存在如下关系:阈值电压越高,cell速度越慢,功耗越小;反之阈值电压越低,cell速度越快,功耗越高。

在实际应用中,一般采用的策略为:对于性能要求高的模块,或者频率比较高的部分,采用Vth比较低的cell,让setup更容易收敛;对于性能要求较低的模块,或者频率较低的部分,多采用Vth比较高的cell,让功耗更低。通过这种方法,可以实现在同一块芯片上,根据性能和功耗的不同要求而调整cell的使用,从而避免在不太重要的功能上浪费过多的功耗。

* **多电压域设计(Multi-Voltage, Power Gating)**

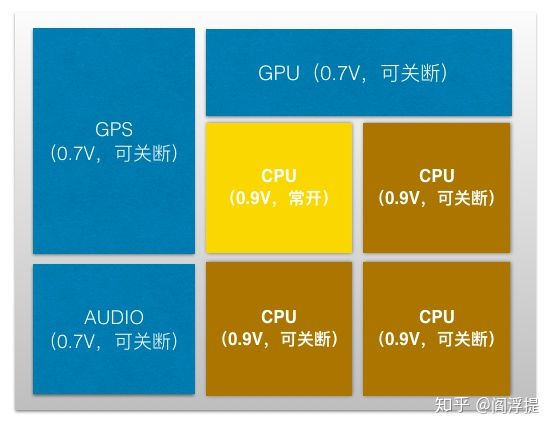

在使用手机的时候,我们经常会遇到这种情况:当我们看到电池快要没电而手头有没有充电设备的时候,我们会尽量关闭所有应用,不再听歌不再看视频,甚至连地图的定位与导航功能都不再开启,其根本目的就在于减少消耗电池的功能。在芯片设计中也引入了这种理念:一颗SoC中可能包含很多功能模块如视频处理(DSP),音频处理(AUDIO),定位(GPS),游戏(GPU),存储(Memory)等,但大多数功能并不会同时开启,因此为了降低不用模块在等待状态下消耗的功耗,干脆就设计成在不用的时候把它们关闭。这就是Power Gating最初的想法。与此同时,对于性能要求较高的CPU,GPU等模块,由于需求频率较高,在设计上可能采用较高的电压,而一些不太核心的模块如AUDIO,GPS等,可以采用相对低的电压来设计。这样一来,整颗芯片可能就会变成下面的样子(下图不影射任何实际芯片):

这样一来,芯片的功耗最低时仅有一个CPU内核处于开启状态,可以大幅度减少其他模块在等待时的电量消耗,从而增加电池使用时间。

尽管它的思路很简单,但是在实际设计中不管是不同电压还是模块关断,都会带来很多额外的问题,这些问题以及业界普遍应用的解决方案我们将在后面的文章中一一提及

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning