在搞芯片设计的公司,而且那个时候公司还买了很多STM32F411的“die”回来自己封装,然后丝印搞上公司的产品,这样就“完美”成为公司的芯片了。

“die”算是一个半成品,如果量大,自己买“die”来封装成芯片,其实单价比买成品还要便宜(之前公司就是这样考虑的,可惜···)。

最开始听他们说“die”我都还不知道是什么意思,后来才知道原来芯片还可以这么搞。

下面就来说说wafer、die、cell这几个专业名词。

什么是waferwafer,即大家所说的“晶圆”,晶圆是指制作硅半导体电路所用的硅晶片,其原始材料是硅。

## wafer

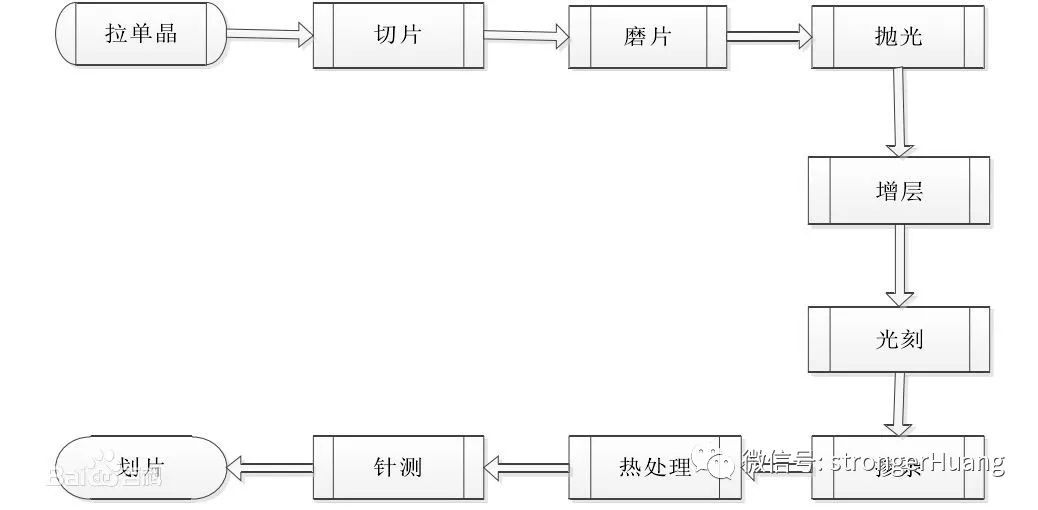

高纯度的多晶硅溶解后掺入硅晶体晶种,然后慢慢拉出,形成圆柱形的单晶硅。硅晶棒在经过研磨,抛光,切片后,形成硅晶圆片,也就是晶圆。

目前国内晶圆生产线以8英寸和12英寸为主。

晶圆的主要加工方式为片加工和批加工,即同时加工1片或多片晶圆。随着半导体特征尺寸越来越小,加工及测量设备越来越先进,使得晶圆加工出现了新的数据特点。

同时,特征尺寸的减小,使得晶圆加工时,空气中的颗粒数对晶圆加工后质量及可靠性的影响增大,而随着洁净的提高,颗粒数也出现了新的数据特点。

## die

什么是die可能有人英语学得好,认为die不就是死亡的意思吗。还有在百度百科中指的是芯片(die泛指为“芯片”)。

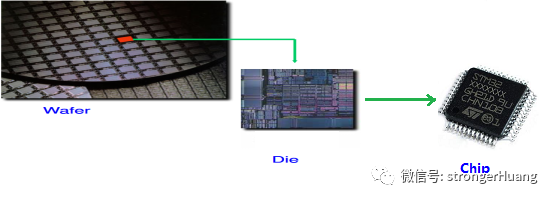

这里说的die指的是晶粒,即晶圆被切割切成的小块,这里学名叫die。

die是硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。

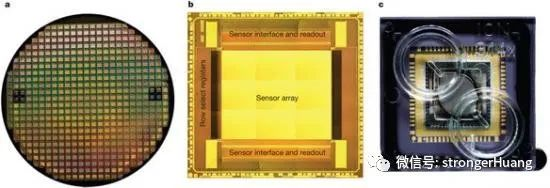

我们解剖芯片之后,就能看见芯片中的die:

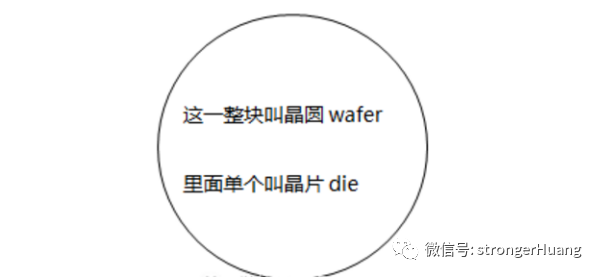

wafer和die的关系好比下面这张图:

## cell

cell在集成电路中的解释为“单元”,比die还要更小级别,通常有这么一个关系:wafer》die》cell

我这里也没有找到明确的解释,翻译过来就是细胞、单元的意思,我大概看的解释为:把die进一步划分为多个cell,比如IO单元、电源管理单元等。

它们的关系和区别wafer为晶圆,由纯硅(Si)构成。一般分为6英寸、8英寸、12英寸规格不等,晶片基于wafer上生产出来。Wafer上一个小块晶片晶圆体学名die,封装后成为一个颗粒。

一片载有NandFlash晶圆的wafer首先经过切割,测试后将完好的、稳定的、足容量的die取下,封装形成日常所见的NandFlash芯片。

wafer和die的关系可以通过一张图来理解:

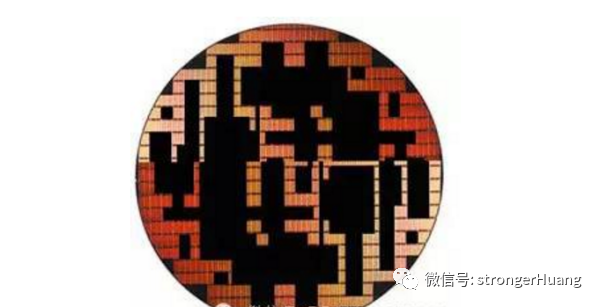

品质合格的die切割下去后,原来的晶圆成了下图的样子,是挑剩下的DowngradeFlashWafer。残余的die是品质不合格的晶圆。黑色的部分是合格的die,会被原厂封装制作为成品NAND颗粒,而不合格的部分,也就是图中留下的部分则当做废品处理掉。

筛选后的wafer

①材料来源方面的区别以硅工艺为例,一般把整片的硅片叫做wafer,通过工艺流程后每一个单元会被划片,封装。在封装前的单个单元的裸片叫做die。chip是对芯片的泛称,有时特指封装好的芯片。

②品质方面的区别品质合格的die切割下去后,原来的晶圆就成了下图的样子,就是挑剩下的DowngradeFlashWafer。这些残余的die,其实是品质不合格的晶圆。被抠走的部分,也就是黑色的部分,是合格的die,会被原厂封装制作为成品NAND颗粒,而不合格的部分,也就是图中留下的部分则当做废品处理掉。

③大小方面的区别封装前的单个单元的裸片叫做die。chip是对芯片的泛称,有时特指封装好的芯片。cell也是单元,但是比die更加小cell《die《chip。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning