静态时序分析的简单定义如下:套用特定的时序模型,针对特定电路分析其是否违反设计者给定的时序限制。

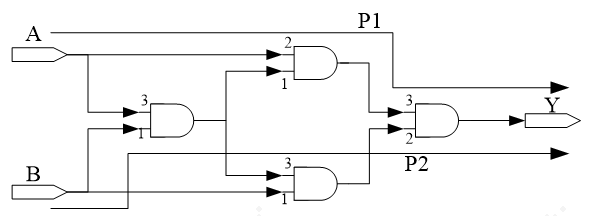

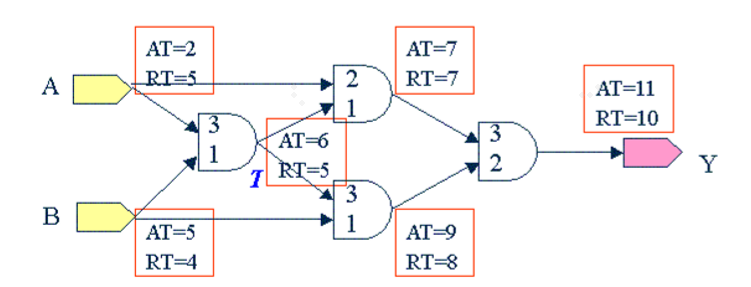

以分析的方式区分,可分为基于路径和基于结点两种,我们采用基于路径的分析方式来说明。如图1所示,信号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y点。套用的时序模型标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。而使用者给定的时序限制为:

(1)信号A到达电路输入端的时刻为2(AT=2,AT为Arrival Time)。

(2)信号B到达电路输入端的时刻为5(AT=5)。

(3)信号必须在时间点10之前到达输出端 Y(RT=10,RT 为 Required Time)。

现在我们针对P1及P2两条路径来做分析。P1的起始点为A,信号到达时刻为2。经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以信号到达此闸输出的时刻为4(2+2)。依此类推,信号经由P1到达输出Y的时刻为7(2+2+3)。在和上述第(3)项时序限制比对之后,我们可以得知对P1这个路径而言,时序是满足使用者要求的,能够正常工作。

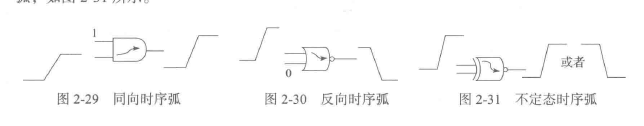

## **时序弧:**

1. 静态时序分析是基于timing arc数据的时序分析。

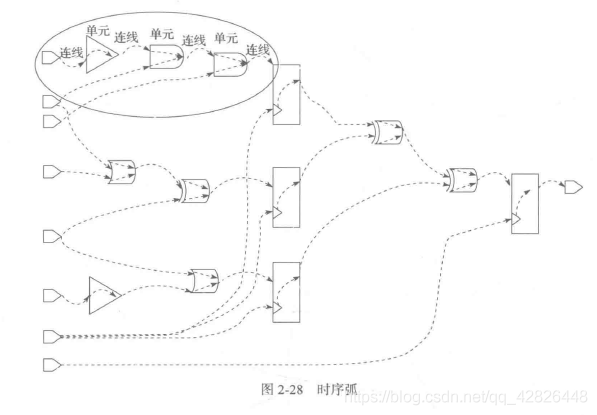

2. 时序弧是用来描述两个节点延时信息的数据,时序弧的信息分为连线延时和单元延时。

3. 连线延时是单元输出端口和删除网络负载之间的延时信息;单元延时是单元输入端口到输出端口的延时信息。因此一条完整路径的时序信息计算由连线延时和单元延时组成。

1. 单元延时的时序弧分为基本时序弧和约束时序弧。

2. 基本时序弧包括组合时序弧、边沿时序弧、复位清零时序弧、三态使能时序弧等。

3. 约束时序弧包括建立时序弧、保持时序弧、 恢复时序弧、移除时序弧和脉冲时序弧/

4. 组合时序弧根据单元功能逻辑的不同,分为3种:

Timing Arc 定义逻辑闸任两 个端点之间的时序关系,其种类有 Combinational Timing Arc(组合时序弧)、Setup Timing Arc(建立时序弧)、 Hold Timing Arc(保持时序弧)、Edge Timing Arc(边沿时序弧)、Preset and Clear Timing Arc(复位清零时序弧)、Recovery Timing Arc(恢复时序弧)、Removal Timing Arc(移除时序弧)、Three State Enable & Disable Timing Arc(三态使能时序弧)、Width Timing Arc。其中第 1、4、5、8 项定义时序延迟,其它各项则是定义时序检查。

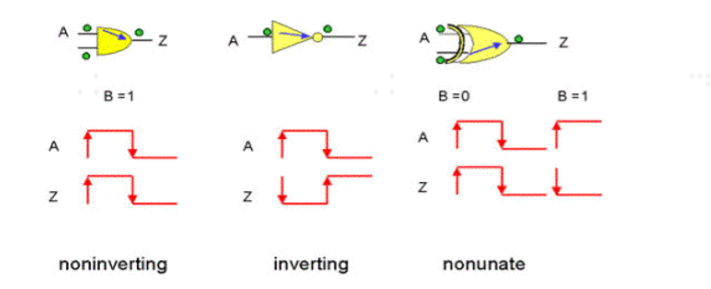

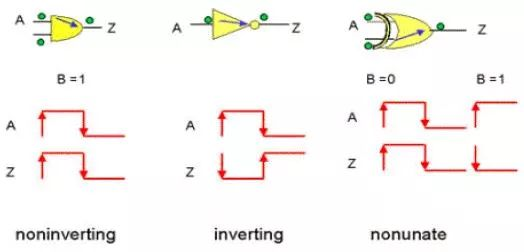

Combinational Timing Arc 的Sense有三种,分别是**inverting**(或 negative unate),**non-inverting**(或 positive unate)以及**non-unate**。

当Timing Arc 相关之特定输出(下图Z)信号变化方向和特定输入(下图A)信号变化方向相反(如输入由0变1,输出由1变0),则此Timing Arc 为inverting sense。反之,输出输入信号变化方向一致的话,则此Timing Arc 为non-inverting sense。当特定输出无法由特定输入单独决定时,此Timing Arc 为non-unate。

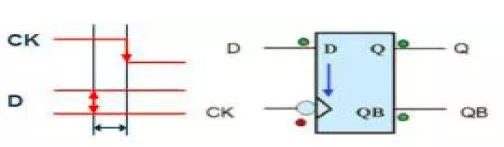

**Setup Timing Arc**:定义时序组件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time,依据Clock上升或下降分为2类

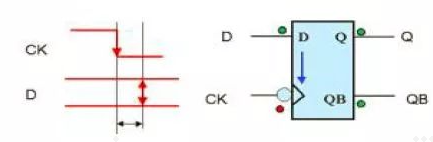

**Hold Timing Arc**:定义时序组件所需的 Hold Time,依据Clock 上升或下降分为2类

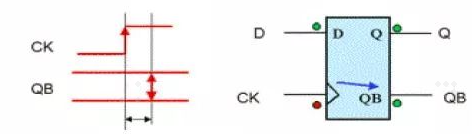

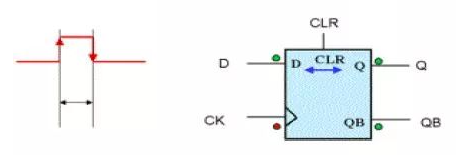

**Edge Timing Arc**:定义时序组件Clock Active Edge 到数据输出的延迟时间,依据Clock上升或下降分为2类

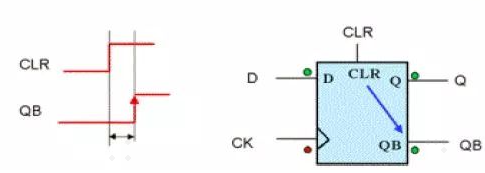

**Preset and Clear Timing Arc**:定义时序组件清除信号(Preset或Clear发生后,数据被清除的速度,依据清除信号上升或下降及是Preset或Clear分为4类

这个Timing Arc 通常会被取消掉,因为它会造成信号路径产生回路,这对STA而言是不允许的

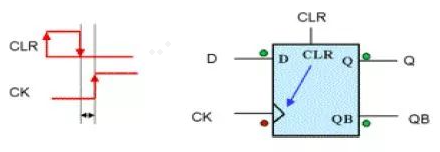

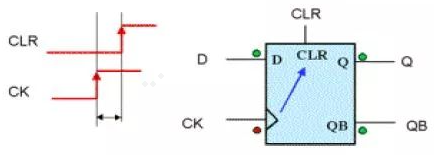

**Recovery Timing Arc**:定义时序组件Clock Active Edge 之前,清除信号不准启动的时间,依据Clock上升或下降分为2类

**Removal Timing Arc**:定义序向组件Clock Active Edge 之后,清除信号不准启动的时间,依据Clock上升或下降分为2类

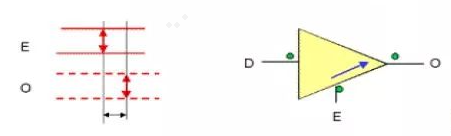

**Three State Enable & Disable Timing Arc**:定义 Tri-State 组件致能信号(Enable)到输出的延迟时间,依据Enable或Disable分为2类

**Width Timing Arc**:定义信号需维持稳定的最短时间,依据信号维持在0或1的位准分为2类

操作环 境指的是制程(Process)、电压(Voltage)、温度(Temperature)三项因子。 这三项因子通常会被简称为 PVT,其对时序的影响可用下方线性方程式来描述。 其中 nom_process、nom_voltage 及 nom_temperature 会定义在标准组件库中, 代表建立时序表格时的操作环境

**静态时序分析技术**是一种穷尽分析方法,它提取整个电路的所有时序路径,通过计算信号沿在路径 上的延时传播找出违反时序约束的错误,主要是检查电路可以正常工作的最大频率、找到电路中的关键路 径、检查各个路径是否满足建立时间和保持时间等、计算各个节点的负载、找到电路中延时最长的连线等. 静态时序分析技术在功能上和性能上都有很大的优越性,所以现在已广泛应用于 VLSI 的时序验证。

时序路径指 的是设计中一个点(开始点)到另一个点(结束点)的序列,开始点一般是时钟端口、输入端口、或寄存器或锁 存器的数据输入引脚等,结束点一般是时钟、输出端口、或寄存器或锁存器的数据输入引脚等

时序例外是指由于某种原因不希望 PrimeTime 检查的路径. 比如,某些路径明显是伪路径,在正常工作 情况下是不可能会经过的;或者,为了加快分析的速度,有些路径我们不希望 PrimeTime 检查. 这些情况下, 我们可以通过设计时序例外来实现

### 有三种方法可以用于定义时序例外:

**set-false-path**:设置伪路径可以忽略在这些路径上进行关键路径、建立时间和保持时间等的检查.

**set-case-analysis**:把某些端口或管脚设为常数,以使得某些路径不被检查.

**set-disable-timing**;使得一些路径上的时序参数(timing arcs)无效,以达到不检查该路径的目的.

系统单芯片(SOC)

芯片(IC)

静态时序分析(Static Timing Analysis 简称 STA)

STA 的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析 其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分 为 Path-Based 及 Block-Based 两种。

## **Block-Based 的分析方式**。

此时时序信息(Timing Information)的储存 不再是以路径为单位,而是以电路节点(Node)为单位。由 Timing Constraint 我们仅 能得知 A 节点的 AT 为 2,B 节点的 AT 为 5 以及 Y 节点的 RT 为 10。Block-Based 的分析 方式会找出每个节点的 AT 和 RT,然后比对这两个数值。当 RT 的值大于 AT 时表示信号 比 Timing Constrain 中要求的时间还早到达,如此则 Timing 是满足的,反之则不满足。

## Timing Constraints:

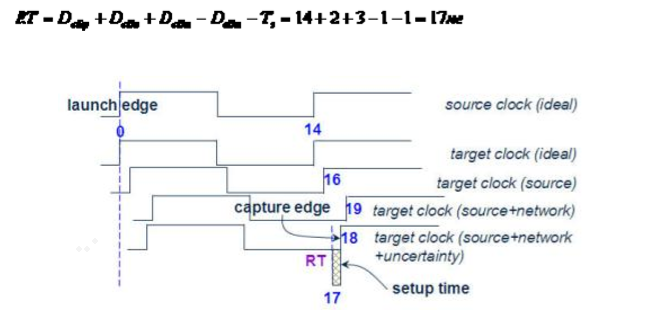

Timing Constraint 为使用者所给定,用来检验设计电路时序的准则。其中 最重要的一项就是频率(Clock)的描述。对于一个同步电路而言,缓存器和缓 存器之间的路径延迟时间必须小于一个 Clock 周期(Period),也就是说,当我 们确认了 Clock 规格,所有缓存器间的路径的 Timing Constraint 就会自动给定 了。

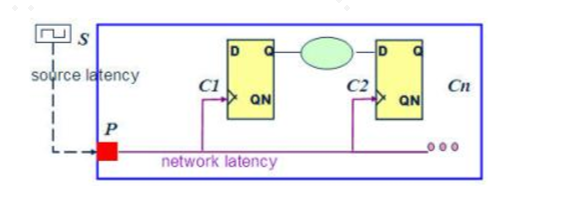

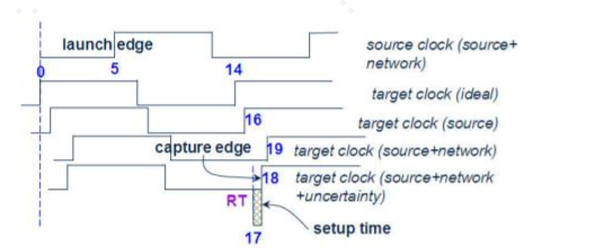

Clock 规格包含波形、Latency 及 Uncertainty 的定义。波形定义一个 Clock 的周期及信号上升缘及下降缘的时间点。Latency 定义从 Clock 来源到序向组件 Clock 输入端的延迟时间。Uncertainty 则定义 Clock 信号到序向组件 Clock 输 入端可能早到或晚到的时间。

**正反器(Flip-Flop)**

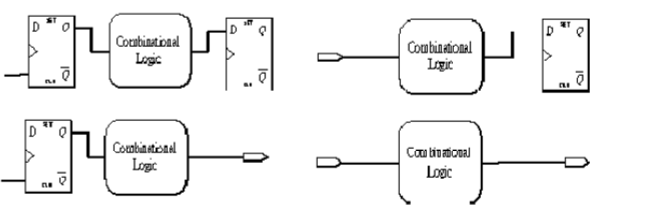

### Path 根据起点及终点可以分为 4 种:

1. 由 Flip-Flop Clock 输入到 Flip-Flop 数据输入(图左上)。

2. 由主要输入(Primary Input,简称 PI)到 Flip-Flop 数据输入(图 右上)。

3. 由 Flip-Flop Clock 输入到主要输出(Primary Output,简称 PO)(图 左下)。

4. 由主要输入到主要输出(图右下)。

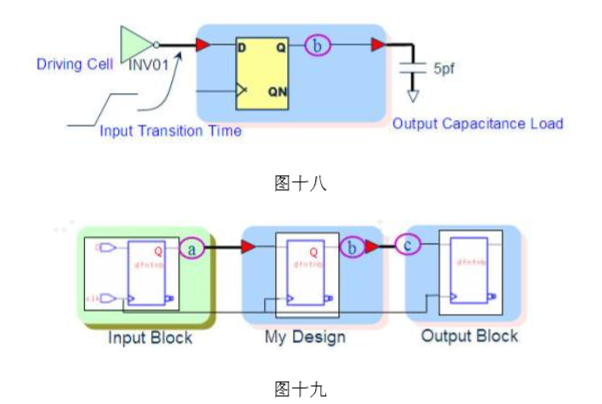

我们会定义下列的 Boundary Condition:

1. Driving Cell:定义输入端点的推动能力(图十八)。

2. Input Transition Time:定义输入端点的转换时间(图十八)。

3. Output Capacitance Load:定义输出负载(图十八)。

4. Input Delay:输入端点相对于某个 Clock 领域的延迟时间。(图十九, Delayclk-Q + a)

5. Output Delay:自输出端点往外看相对于某个 Clock 领域的延迟时间。 (图十九,c)

加上 Boundary Condition 后,只要 Clock 给定,所有 Path 的 Timing Constraint 就会自动给定。

由于每个 Path 都有 Timing Constraint,所以时序分析都能够进行。但在 某些情况下,有些 Path 的分析可能没有意义,因此妳会想忽略这些 Path 的分析。 或是有些 Path 分析的方式不一样,妳会想指定这些 Path 的分析方式。此时就要 设定一些 Timing Exception,如 False Path 和 Multi-cycle Path 等等来处理 非一般性的时序分析。

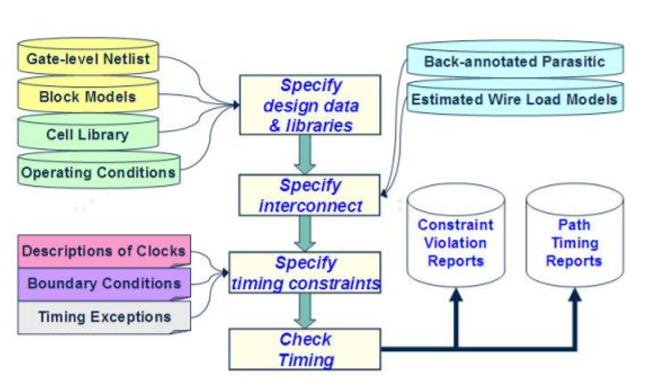

#### STA 的流程

## Step-By-Step 的方式说明时序分析的方式

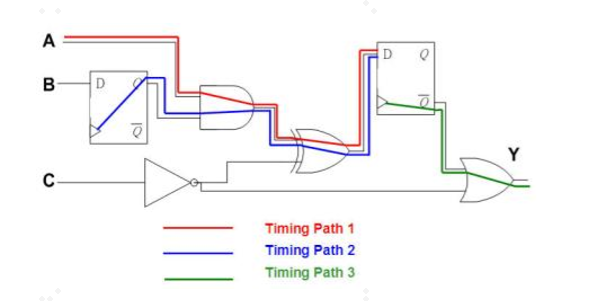

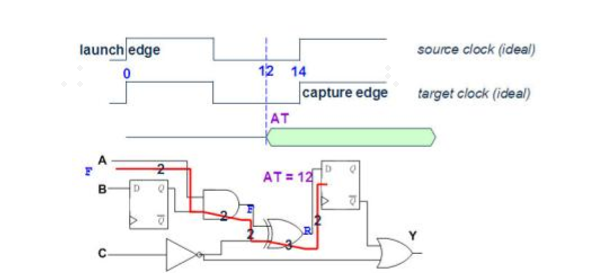

1. 首先找出所有 Timing Path,我们只列出具代表性的 3 条 Timing Path 来 加以说明。

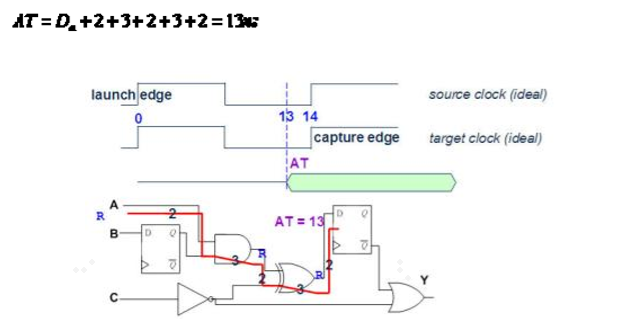

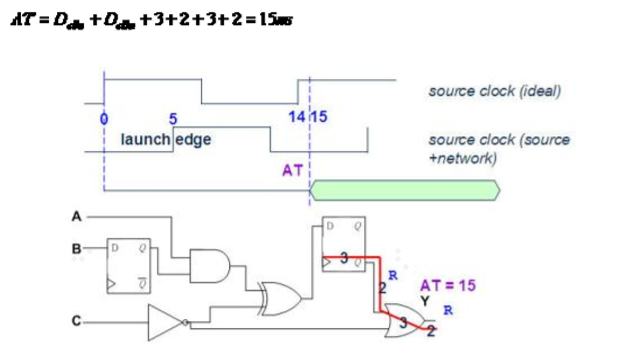

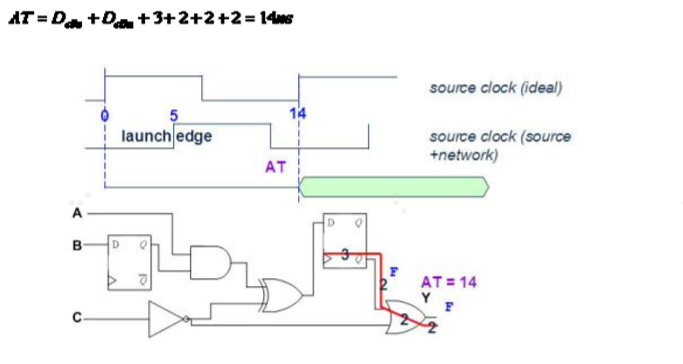

2. 假设输入 A 信号由 0 变 1,计算第 1 条 Path 终点信号到达的时间(Arrival Time 简称 AT)。

3. 假设输入 A 信号由 1 变 0,计算第 1 条 Path 终点 AT

4. 计算第 1 条 Path 终点的需求时间(Required Time,简称 RT)

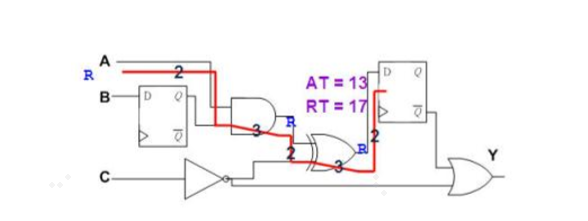

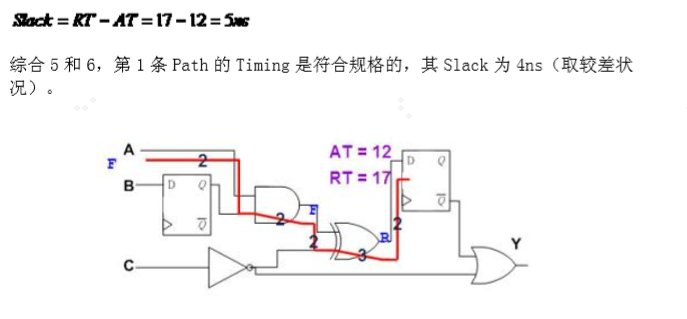

5. 假设输入 A 信号由 0 变 1,计算第 1 条 Path 终点的 Slack。Slack 等于 RT 和 AT 的差值,对于 Setup Time 验证来说等于 RT - AT,对于 Hold Time 验 证来说等于 AT - RT。在此 Setup Time 范例中,Slack 为正,表示信号实际 到达 Path 终点时间比必须到达的时间还早,因此 Timing 是满足的。

6. 假设输入 A 信号由 1 变 0,计算第 1 条Path 终点的 Slack。Slack 为正, 因此 Timing 是满足的。

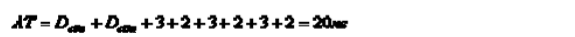

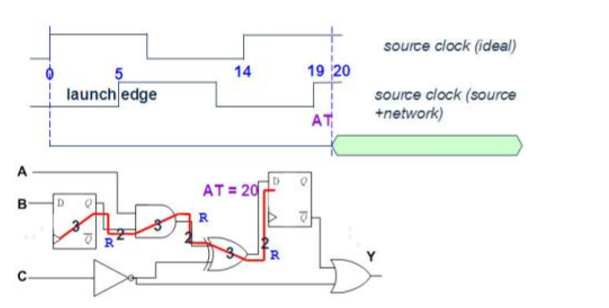

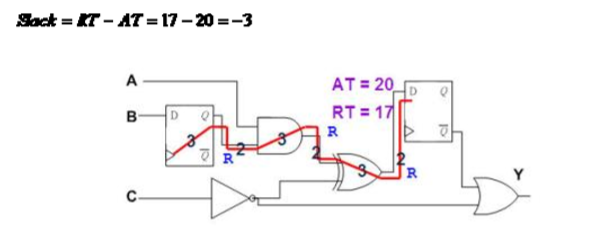

7. 假设前级 Flip-Flop 的信号由 0 变 1,计算第 2 条 Path 终点的 AT

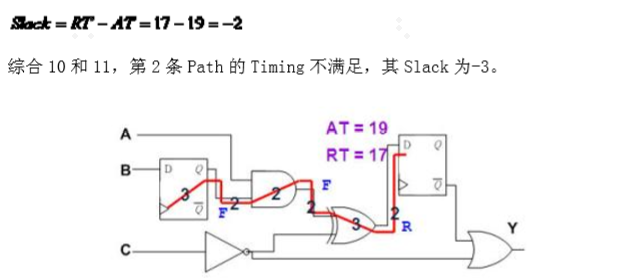

8. 假设前级 Flip-Flop 的信号由 1 变 0,计算第 2 条 Path 终点的 AT。

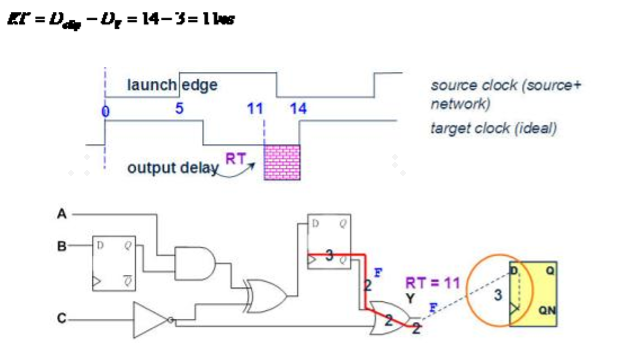

9. 计算第 2 条 Path 终点的 RT。

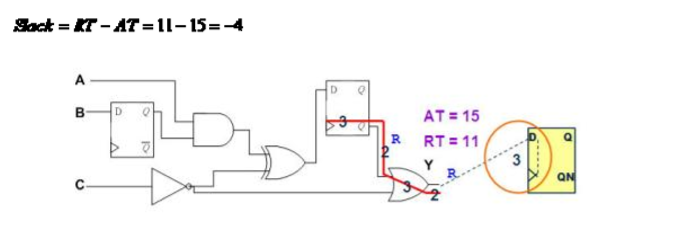

10. 假设前级 Flip-Flop 的信号由 0 变 1,计算第 2 条 Path 终点的 Slack。Slack 为负,因此 Timing 不满足。

11. 假设前级 Flip-Flop 的信号由 1 变 0,计算第 2 条 Path 终点的 Slack。Slack 为负,因此 Timing 不满足。

12.假设前级 Flip-Flop 的信号由 0 变 1,计算第 3 条 Path 终点的 AT

13. 假设前级 Flip-Flop 的信号由 1 变 0,计算第 3 条 Path 终点的 AT

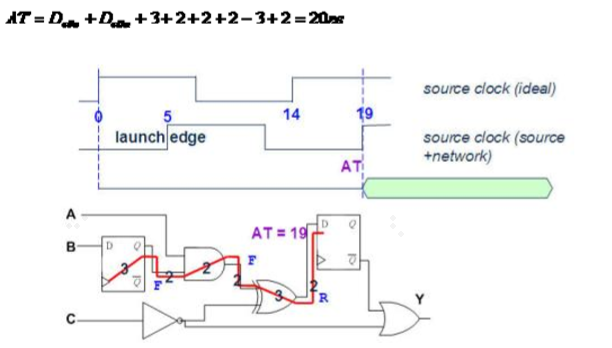

14. 计算第 3 条 Path 终点的 RT

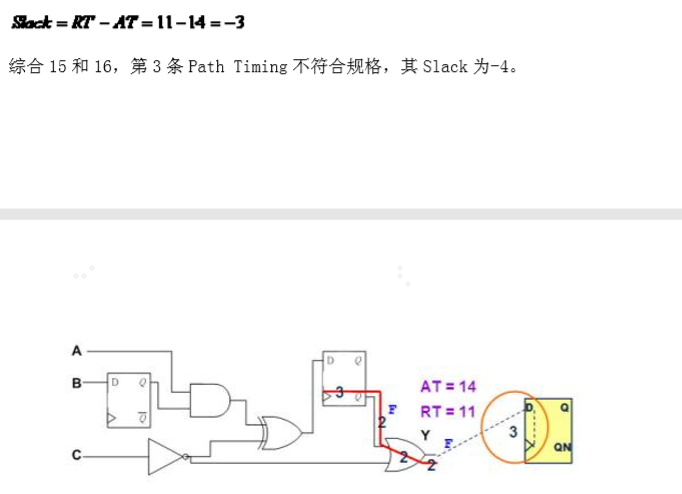

15. 假设前级 Flip-Flop 的信号由 0 变 1,计算第 3 条 Path 终点的 Slack。Slack 为负,因此 Timing 不满足

16. 假设前级 Flip-Flop 的信号由 1 变 0,计算第 3 条 Path 终点的 Slack。Slack 为负,因此 Timing 不满足。

综合上述分析结果,此电路的时序不符合规格,其 Critical Path 是 Path3, Slack 为-4。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning