**SDC**. 全称**Synopsys design constraints**. SDC是一个设计中至关重要的一个文件。它对电路的时序,面积,功耗进行约束,它是设计的命脉,决定了芯片是否满足设计要求的规范。Timing工程师在release sdc时必须非常小心,一个错误的false path或者case constant就有可能导致整块芯片不工作。

Timing Constraint 为使用者所给定,用来检验设计电路时序的准则。我们在做STA前首先要了解各种约束是做什么的。

Timing Constraint按照它们的用途,大致分为以下几类:

(1)描述芯片的工作速度,即时钟的频率,包括**create_clock,create_generated_clock**等

(2)描述芯片的边界约束,包括**set_input_delay, set_output_delay**等

(3)描述芯片的一些设计违反rule(DRV),包括**set_max_fanout,set_max_capacitance, set_max_transition**等

(4)描述设计中一些特殊的路径,包括**set_false_path,set_multicycle_path**等

(5)描述设计中一些需要禁止的timing arc,例如**set_disable_timing**

需要注意的是,设计的不同阶段我们使用的sdc都有所不同(当然,有的公司比较强大,会有一套golden sdc)。比如说,综合时由于模型的粗糙,我们会选择过约sdc,将时钟频率设得更高一些;CTS之前,由于skew的不确定性,通常我们也会加大uncertainty;还有signoff tool与PR工具correlation问题,margin的设置也会不一样。

那我们如何去合理定义一个设计的sdc呢?

这是一项非常有难度的工作,其实常用的sdc命令就以下几条,但要准确运用他们可不容易。

**clock相关**:

create_clock

create_generated_clock

set_clock_uncertainty

set_clock_groups

set_input_delay

set_output_delay

**系统接口相关**:

set_input_transition

set_load

set_driving_cell

**时序特例相关:**

set_false_path

set_multicycle_path

**逻辑赋值相关:**

set_case_analysis

接下来几篇文章会分别介绍这些命令

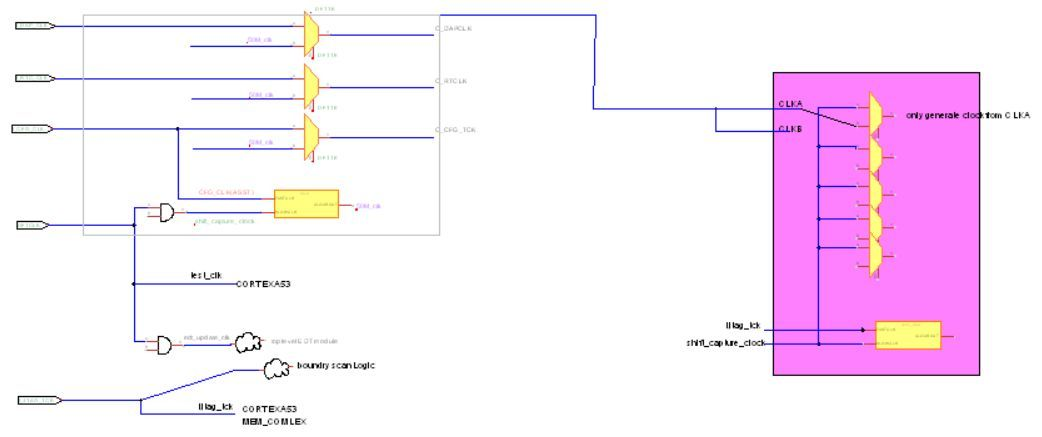

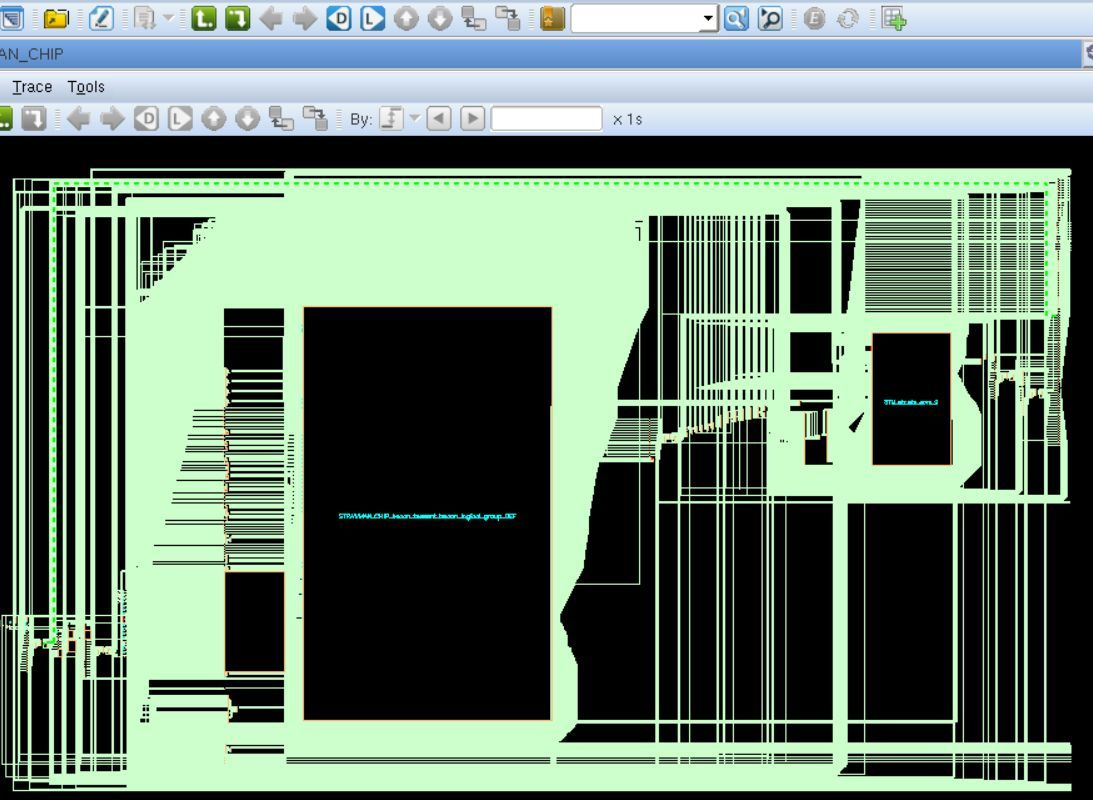

还有一个最重要的前提条件是:我们必须要尽早有一张结构清晰的clock结构图。而且是越早做越好。clock结构最好是让前端设计人员给你,当然也可以通过cad软件自己去画一张。这边介绍一个比较好用的绿色小软件**TinyCad**. 简单易学~~

也可以通过**Verdi**来trace电路结构,这也是很方便的,只需要读入设计的网表就行

好了,今天就大致介绍一下sdc的基本概念,以后会分别介绍几个重要的sdc命令。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning