PTPX在功耗分析中的作用

当今,随着工艺的越来越深入,芯片的漏电也变得越来越大。而且芯片的性能也越来越高,如之前的matrix只要几十Mhz,现在都需要上百Mhz这样的频率。而且CPU/GPU的主频也变得越来越高。又由于现在人们越来越讲究电池的续航能力,无论是手持设备,还是笔记本,人们都希望自己的电子设备待机时间越长越好。所以,种种原因,降低功耗提高到了一个空前的关注度。

那么,本文就相关PTPX在功耗分析中的作用,稍微简述一下。

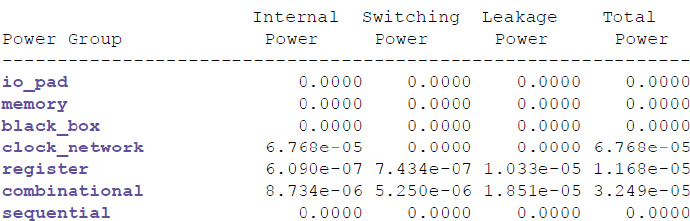

首先,功耗大致包括total power = leakage power +internal power + switching power。其中internal power + switch power = dynamic power.

Leakage power,即漏电功耗和本身工艺库特性相关,后端可以对non-crtical path进行cell的替换,从LVTàSVT,SVTàHVT,HVTàUHVT。另外,也可以对设计进行划分power domain。当这个模块不工作的时候,可以进行断电。从而大大降低芯片的漏电功耗。

Internal power,即短路功耗,即上下PMOS和NMOS同时导通时的功耗。当物理上cell驱动transition time很差的时候,会导致chip的internal power有异样。

Switch power,即开关功耗。动态功耗和data的翻转率(TR),静态概率(SP),电压,负载电容相关。一般情况下,需要读入SPEF文件,从而抽取每个节点上的RC参数用于计算switch power。

第二,我们可以设置以下命令可以让PrimeTime进入功耗分析模式:

set power\_enable\_analysis true

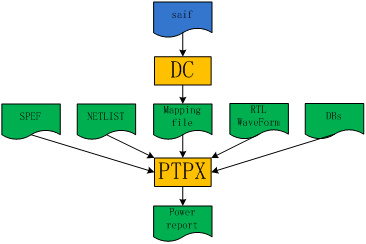

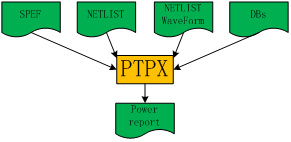

PTPX可以在设计的不同阶段,可以采用不同的模式进行功耗的分析。下面提供PTPX两种不同的流程。方式一比较适合大型设计,大型设计的后端都比较难出,所以采用RTL的waveform,通过PTPX的propagation算法,自动推导出netlist上每个节点的翻转,即(TR,SP),进而得到功耗。另外也非常适合在设计的早期阶段,评估和计算设计中的功耗。方式二,比较适合小型设计。另外加上后仿波形相对容易获取,那么可以采用方式二获得功耗值。方式二相比方式一在功耗值上更接近芯片回片真实值。

第三,从PTPX中我们可以获取average power和time-based power.

从Average power中我们可以获取clk tree power,这是我们关注的重点。经验值告诉我们,在重负载情况下,clk tree power占据1/3total power。对于Combinational power,根据经验,对于大型算法模块,如通信算法,图像处理ISP等。在RTL阶段可能看不出power的异样,一旦加入SDF就会发现power成倍增加,这是大家小心的地方。

下面是time\-based power曲线图,可以看出整个数据发包,收包,解包过程的功耗变化趋势。

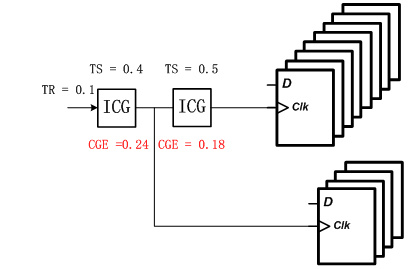

第四,PTPX不仅能够提供功耗值,还能利用PTPX找出功耗为什么过大的原因。主要利用的特性为clock gating efficiency,clock gating ratio以及register gating efficiency。 经验表明,提高CGE,可以高效的对功耗进行优化。下图为一个CGE的概括图,CGE和clock-gating cell后面带的filp-flop的个数,以及CG cell本身的toggle rate saving系数相关。

综上,可以使用PTPX的average power、time-based power、clock gating efficiency、clock gating ratio、Q/CP等feature对设计进行功耗的评估,给出功耗优化的指导方向。

- 电子元器件

- 电阻

- 电容器

- 电感

- 保险丝

- 二极管

- 三极管

- 接插件

- 蜂鸣器

- MOS

- 集成电器基础知识

- 接地的基础知识

- STA

- Skew

- setup和hold

- 问题

- timing path

- Latency

- 跨时钟域的代码检查(spyglass)

- 时间换算

- 名词解释

- 寄存器

- 触发器

- ECO

- 通用芯片和嵌入式芯片有什么区别

- Signoff

- SOC

- VLSI

- NPU

- DDR

- ISP

- Fan-in 和 Fan-out

- 逻辑阈值

- Floorplan

- 寄存器传输的设计(RTL)

- 集成电路设计方法

- Design Rules of Thumb

- Dealing with Resistance

- 芯片设计

- 什么是Scenario?

- 晶圆BUMP加工工艺和原理

- wafer、die、cell

- DFT

- 前端-QC

- CDC

- SDC

- MBIST

- RDC

- Lint

- overview

- PV

- PBA/GPA

- Corner

- PVT

- latency与delay区别

- Power

- LVT, RVT, HVT 的区别

- PPA

- RTL

- 芯片行业的IP是指什么?

- 晶振与晶体的区别

- PLL (锁相环(PhaseLockedLoop))

- 奇偶分频电路

- inverter

- glitch (电子脉冲)

- Power

- Clock Gating

- 低功耗设计

- UPF

- 低功耗单元库

- Power intent

- 亚稳态

- 芯片流程

- 芯片软件

- 亚稳态&MTBF&同步器&AFIFO

- glitch free的时钟切换技术

- max_transition

- MUX

- STA之RC Corner

- process corner 和 PVT

- ICC Scenario Definition

- 寄生电路?

- 晶振

- 信号完整性

- 什么是脉冲?什么是电平?

- 阈值电压

- bump

- IC设计常用文件及格式介绍

- 文件格式

- spef

- 后端

- phy芯片的作用

- MIPI简介

- 异步桥

- 芯片后仿之SDF

- 慕课-VLSI设计基础(数字集成电路设计基础)

- 概论

- MOS晶体管原理

- 设计与工艺接口

- 反相器和组合逻辑电路

- 问题trainning