## 一、 Linux版本

` `linux下的硬件仿真工具VCS, NC, Questasim都是商业软件,如果想自己在自己机器上跑点小例子,那么通常人就需要去破解这些商业软件。这些年版权的意识越来越强,破解真不是一个好方法。不如使用一些开源的仿真器,来跑自己的小例子。本文要讲的iverilog是目前开源仿真器的不二选择。

## 安装

` `首先安装好git, 如果没有就是官方网站直接下载压缩包后,再解压缩。

```

git clone https://github.com/steveicarus/iverilog.git

cd iverilog

sh autoconf.sh

./configure && make && make install

```

` `但一般不会这么顺利的。

有心人会发现在iverilog目前下没有configure文件,所以不知道怎么办,其实只要去官方网站上看一下就明白它是用autoconf.sh来生成configure文件的。

但我一开始执行会报错,原因是少了gperf

可以从下面[链接](https://ftp.gnu.org/gnu/gperf/gperf-3.1.tar.gz)下载源码 然后解压缩, 执行`./configure && make && make install`就可以了当然如果还有错要去装一下autoconf。

### 使用

` `总体来讲,iverilog和其实simulator没大区别,就是先编译,然后运行。 选项大约有

| 选项 | 说明 |

| --- | --- |

| \-D macro\[=def \] | 定义宏 |

| \-I incdir | 等同于-incdir |

| \-o filename | 指定输出的可执行文件名 |

| \-s topmodule | 等同于-top |

| \-y libdir | 等同于-y |

` `比如`iverilog -s top -o cnt top.v cnt.v

vpp cnt`

### 波形

` `可以使用下面代码

```

initial

begin

$dumpfile("test.vcd");

$dumpvars(0,top);

end

```

` `来dump波形, 然后用gtkwave来查看

gtkwave是开源的查看波形的软件,需要单独安装。

` `iverilog主要是一个仿真器,它的不足在于没有调试器,一般商业调试器如NC集成的simvision, VCS集成的DVE, 或者单独的软件verdi。不过只进行学习, iverilog也足够了。复杂的场景还是在公司里跑的吧。

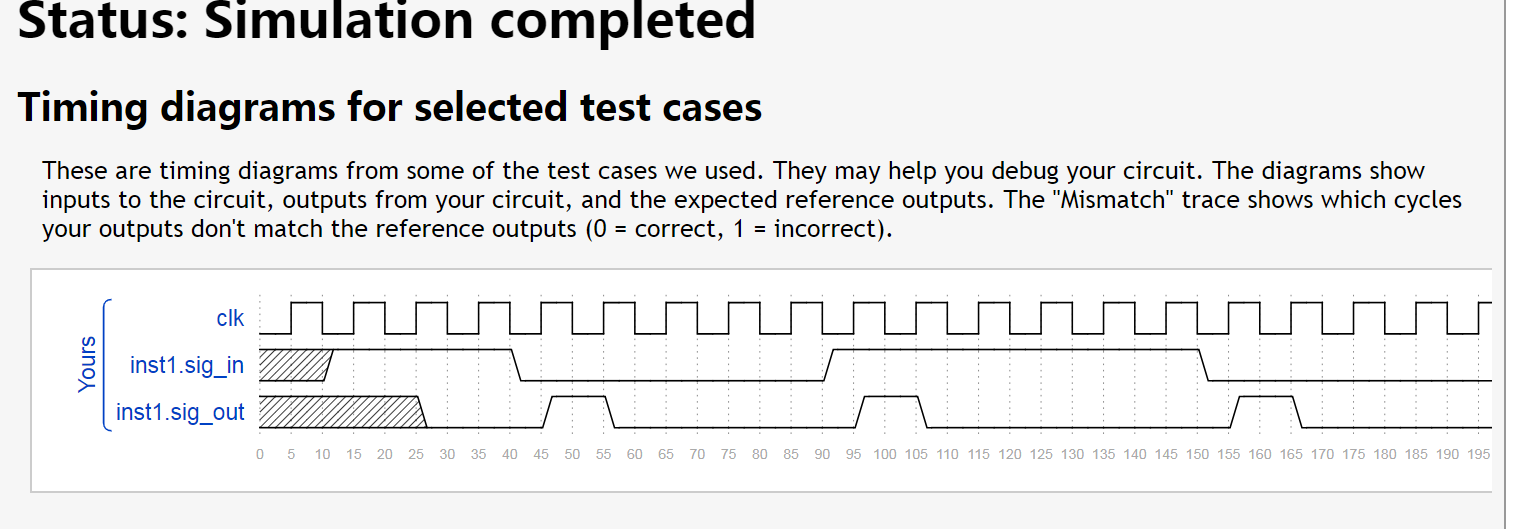

## 二、网页版

` `网址为[iverilog网页版](https://hdlbits.01xz.net/wiki/Iverilog)。

` `网页版非常适合验证。使用方便,强烈推荐。

## 三、linux上的自用仿真脚本

为了方便使用iverilog进行仿真,写了一个在linux上使用的脚本,脚本可以提供`testbech`模板,可以自动编译和仿真项目,并自动打开gtkwave,以查看波形。</br>

脚本代码如下:

```bash

#!/bin/bash

#UFUNCTION=iverilog个人仿真脚本

#by yunahp 2020/6/4

####################### iverilog仿真脚本 #######################

dir=$(pwd)

if [ "$1" = "-help" ] || [ "$1" = "-h" ];then #帮助

echo "Usage : mvsim [option]"

echo " mvsim 仿真波形显示一条龙服务"

echo " mvsim -init 生成iverilog testbech模板"

echo " mvsim -help 帮助"

echo " mvsim -r 刷新仿真波形文件"

echo " mvsim -m module 创建module.v文件"

echo " mvsim -sm module 创建module.sv文件"

echo

exit 0

fi

if [ "$1" = "-init" ] || [ "$1" = "-i" ];then #生成iverilog testbech模板

if [ ! -f run ];then

echo "#!/bin/bash" > run

echo "mvsim \$*" >> run

chmod +x run

echo "info:已生成run脚本"

fi

if [ -f tb.v ];then

echo "fail:初始化失败,已存在tb.v文件!"

exit 0

fi

cat <<EOF >tb.v

\`timescale 1ns / 1ps

module tb ;

reg clk,rst;

//生成始时钟

parameter NCLK = 4;

initial begin

clk=0;

forever clk=#(NCLK/2) ~clk;

end

/****************** BEGIN ADD module inst ******************/

//Modulenamme top (rst,clk);

/****************** BEGIN END module inst ******************/

initial begin

\$dumpfile("wave.lxt2");

\$dumpvars(0, tb); //dumpvars(深度, 实例化模块1,实例化模块2,.....)

end

initial begin

rst = 1;

#(NCLK) rst=0;

#(NCLK) rst=1; //复位信号

repeat(100) @(posedge clk)begin

end

\$display("运行结束!");

\$dumpflush;

\$finish;

\$stop;

end

endmodule

EOF

echo "info:已生成tb.v文件!"

exit 0

fi

# verilog模板

if [ "$1" = "-m" ];then #添加module

if [ "x$2" = "x" ];then

echo "error:输入的命令有误,请查看帮助!"

else

file="$2.v"

if [ -f $file ];then

echo "error:$file已存在!"

exit 1

fi

dat=$(date +%Y/%m/%d)

echo "// ********************************************************************">$file

echo "// File name : $file">>$file

echo "// Module name : $2">>$file

echo "// Author : hpy">>$file

echo "// Description : ">>$file

echo "// Date : $dat">>$file

echo "// --------------------------------------------------------------------">>$file

echo "module $2(" >> $file

echo " input clk,">>$file

echo " input rst_n">>$file

echo ");">>$file

echo "">>$file

echo "always@(posedge clk or negedge rst_n)">>$file

echo "begin">>$file

echo " if(!rst_n)begin">>$file

echo "">>$file

echo " end">>$file

echo " else begin">>$file

echo "">>$file

echo " end">>$file

echo "end">>$file

echo -e "\nendmodule\n">>$file

echo "info:$file生成成功!"

fi

exit 0

fi

# system verilog模板

if [ "$1" = "-sm" ];then #添加module

if [ "x$2" = "x" ];then

echo "error:输入的命令有误,请查看帮助!"

else

file="$2.sv"

if [ -f $file ];then

echo "error:$file已存在!"

exit 1

fi

dat=$(date +%Y/%m/%d)

echo "// ********************************************************************">$file

echo "// File name : $file">>$file

echo "// Module name : $2">>$file

echo "// Author : hpy">>$file

echo "// Description : ">>$file

echo "// Date : $dat">>$file

echo "// --------------------------------------------------------------------">>$file

echo "//type=sv" >> $file

echo "//title=demo" >> $file

echo "module $2(" >> $file

echo ");">>$file

echo "">>$file

echo "initial begin" >> $file

echo "" >> $file

echo "end" >> $file

echo "" >> $file

echo "endmodule" >> $file

echo "info:$file生成成功!"

fi

exit 0

fi

if [ $# -gt 0 ];then

if [ "$1" = "-r" ];then

echo "开始仿真!"

else

echo "命令有误,输入mvsim -help 显示帮助!"

exit 1

fi

fi

if [ ! -d sim ];then

mkdir sim

fi

echo "MVSIM info:当前仿真的工程路径为$dir"

rm -rf ./sim/* #清空sim文件夹下的内容

ctags -R

src=$(find -name "*.v")

iverilog -o sim/wave $src #综合verilog代码

cd sim

echo

echo "<<<<<<<<<< S I M R E P O R T >>>>>>>>>>"

vvp -n wave -lxt2 #仿真

echo "<<<<<<<<<<<<<<<<< E N D >>>>>>>>>>>>>>>>"

cd ..

if [ "$1" = "-r" ];then #刷新仿真数据

echo "info:刷新仿真数据,如若刷新成功请自行打开gtkwave查看波形或者刷新已经打开的本工程gtkwave!"

exit 0

fi

gtkwave sim/wave.lxt2 &> /dev/null & #显示波形

exit 0

```

</br>

我将上述脚本命名为`mvsim`,并将这个脚本的路径添加到环境变量中,我的选择是直接将该脚本放到`~/bin`目录下,一般linux在启动时,如果用户目录`~/bin`存在,将会自动添加到环境变量,因此直接将这个文件放到bin下就可以直接使用了。

----

下面是使用该脚本新建一个工程,并自动添加testbech文件,并仿真的一个演示:

</br>

脚本使用`mvsim -i`进行初始化,会生成testbech仿真文件,工程中不加其他模块,初始化后可以直接进行仿真,使用`mvsim`编译工程,并打开波形查看。可以使用帮助参数显示帮助:

```

yhp@yhp-PC ~/Desktop> mvsim -h

Usage : mvsim [option]

mvsim 仿真波形显示一条龙服务

mvsim -init 生成iverilog testbech模板

mvsim -help 帮助

mvsim -r 刷新仿真波形文件

mvsim -m module 创建module.v文件

mvsim -sm module 创建module.sv文件

```

- 序

- 第1章 Linux下开发FPGA

- 1.1 Linux下安装diamond

- 1.2 使用轻量级linux仿真工具iverilog

- 1.3 使用linux shell来读写串口

- 1.4 嵌入式上的linux

- 设备数教程

- linux C 标准库文档

- linux 网络编程

- 开机启动流程

- 1.5 linux上实现与树莓派,FPGA等通信的串口脚本

- 第2章 Intel FPGA的使用

- 2.1 特别注意

- 2.2 高级应用开发流程

- 2.2.1 生成二进制bit流rbf

- 2.2.2 制作Preloader Image

- 2.2.2.1 生成BSP文件

- 2.2.2.2 编译preloader和uboot

- 2.2.2.3 更新SD的preloader和uboot

- 2.3 HPS使用

- 2.3.1 通过JTAG下载代码

- 2.3.2 HPS软件部分开发

- 2.3 quartus中IP核的使用

- 2.3.1 Intel中RS232串口IP的使用

- 2.4 一些问题的解决方法

- 2.4.1 关于引脚的复用的综合出错

- 第3章 关于C/C++的一些语法

- 3.1 C中数组作为形参不传长度

- 3.2 汇编中JUMP和CALL的区别

- 3.3 c++中map的使用

- 3.4 链表的一些应用

- 3.5 vector的使用

- 3.6 使用C实现一个简单的FIFO

- 3.6.1 循环队列

- 3.7 C语言不定长参数

- 3.8 AD采样计算同频信号的相位差

- 3.9 使用C实现栈

- 3.10 增量式PID

- 第4章 Xilinx的FPGA使用

- 4.1 Alinx使用中的一些问题及解决方法

- 4.1.1 在Genarate Bitstream时提示没有name.tcl

- 4.1.2 利用verilog求位宽

- 4.1.3 vivado中AXI写DDR说明

- 4.1.4 zynq中AXI GPIO中断问题

- 4.1.5 关于时序约束

- 4.1.6 zynq的PS端利用串口接收电脑的数据

- 4.1.7 SDK启动出错的解决方法

- 4.1.8 让工具综合是不优化某一模块的方法

- 4.1.9 固化程序(双核)

- 4.1.10 分配引脚时的问题

- 4.1.11 vivado仿真时相对文件路径的问题

- 4.2 GCC使用Attribute分配空间给变量

- 4.3 关于Zynq的DDR写入byte和word的方法

- 4.4 常用模块

- 4.4.1 I2S接收串转并

- 4.5 时钟约束

- 4.5.1 时钟约束

- 4.6 VIVADO使用

- 4.6.1 使用vivado进行仿真

- 4.7 关于PicoBlaze软核的使用

- 4.8 vivado一些IP的使用

- 4.8.1 float-point浮点单元的使用

- 4.10 zynq的双核中断

- 第5章 FPGA的那些好用的工具

- 5.1 iverilog

- 5.2 Arduino串口绘图器工具

- 5.3 LabVIEW

- 5.4 FPGA开发实用小工具

- 5.5 Linux下绘制时序图软件

- 5.6 verilog和VHDL相互转换工具

- 5.7 linux下搭建轻量易用的verilog仿真环境

- 5.8 VCS仿真verilog并查看波形

- 5.9 Verilog开源的综合工具-Yosys

- 5.10 sublim text3编辑器配置verilog编辑环境

- 5.11 在线工具

- 真值表 -> 逻辑表达式

- 5.12 Modelsim使用命令仿真

- 5.13 使用TCL实现的个人仿真脚本

- 5.14 在cygwin下使用命令行下载arduino代码到开发板

- 5.15 STM32开发

- 5.15.1 安装Atollic TrueSTUDIO for STM32

- 5.15.2 LED闪烁吧

- 5.15.3 模拟U盘

- 第6章 底层实现

- 6.1 硬件实现加法的流程

- 6.2 硬件实现乘法器

- 6.3 UART实现

- 6.3.1 通用串口发送模块

- 6.4 二进制数转BCD码

- 6.5 基本开源资源

- 6.5.1 深度资源

- 6.5.2 FreeCore资源集合

- 第7章 常用模块

- 7.1 温湿度传感器DHT11的verilog驱动

- 7.2 DAC7631驱动(verilog)

- 7.3 按键消抖

- 7.4 小脚丫数码管显示

- 7.5 verilog实现任意人数表决器

- 7.6 基本模块head.v

- 7.7 四相八拍步进电机驱动

- 7.8 单片机部分

- 7.8.1 I2C OLED驱动

- 第8章 verilog 扫盲区

- 8.1 时序电路中数据的读写

- 8.2 从RTL角度来看verilog中=和<=的区别

- 8.3 case和casez的区别

- 8.4 关于参数的传递与读取(paramter)

- 8.5 关于符号优先级

- 第9章 verilog中的一些语法使用

- 9.1 可综合的repeat

- 第10章 system verilog

- 10.1 简介

- 10.2 推荐demo学习网址

- 10.3 VCS在linux上环境的搭建

- 10.4 deepin15.11(linux)下搭建system verilog的vcs仿真环境

- 10.5 linux上使用vcs写的脚本仿真管理

- 10.6 system verilog基本语法

- 10.6.1 数据类型

- 10.6.2 枚举与字符串

- 第11章 tcl/tk的使用

- 11.1 使用Tcl/Tk

- 11.2 tcl基本语法教程

- 11.3 Tk的基本语法

- 11.3.1 建立按钮

- 11.3.2 复选框

- 11.3.3 单选框

- 11.3.4 标签

- 11.3.5 建立信息

- 11.3.6 建立输入框

- 11.3.7 旋转框

- 11.3.8 框架

- 11.3.9 标签框架

- 11.3.10 将窗口小部件分配到框架/标签框架

- 11.3.11 建立新的上层窗口

- 11.3.12 建立菜单

- 11.3.13 上层窗口建立菜单

- 11.3.14 建立滚动条

- 11.4 窗口管理器

- 11.5 一些学习的脚本

- 11.6 一些常用的操作语法实现

- 11.6.1 删除同一后缀的文件

- 11.7 在Lattice的Diamond中使用tcl

- 第12章 FPGA的重要知识

- 12.1 面积与速度的平衡与互换

- 12.2 硬件原则

- 12.3 系统原则

- 12.4 同步设计原则

- 12.5 乒乓操作

- 12.6 串并转换设计技巧

- 12.7 流水线操作设计思想

- 12.8 数据接口的同步方法

- 第13章 小项目

- 13.1 数字滤波器

- 13.2 FIFO

- 13.3 一个精简的CPU( mini-mcu )

- 13.3.1 基本功能实现

- 13.3.2 中断添加

- 13.3.3 使用中断实现流水灯(实际硬件验证)

- 13.3.4 综合一点的应用示例

- 13.4.5 使用flex开发汇编编译器

- 13.4.5 linux--Flex and Bison

- 13.4 有符号数转单精度浮点数

- 13.5 串口调试FPGA模板