[TOC]

## windows环境下的配置

sublime text是一款很强大的编辑器,并且跨平台,配合ctag可以实现verilog代码的跳转,就如同查看c函数一样方便。 <br/>

### 1、安装sublim text3

浏览器直接搜索`sublime text3 `下载对应的安装版本安装即可。

### 2、包管理工具

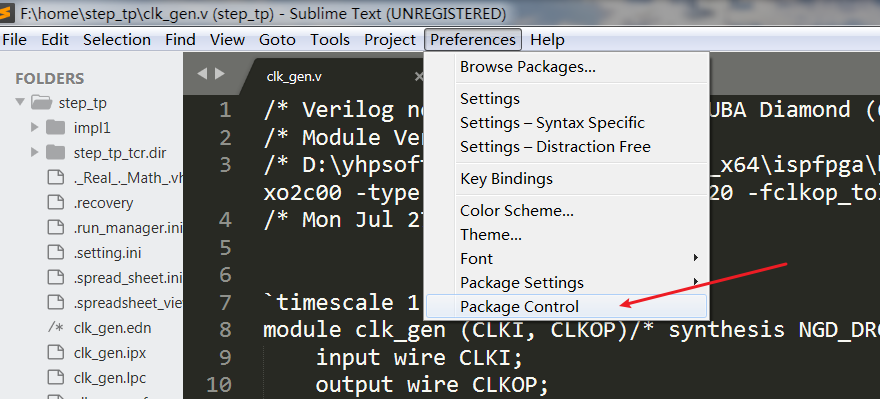

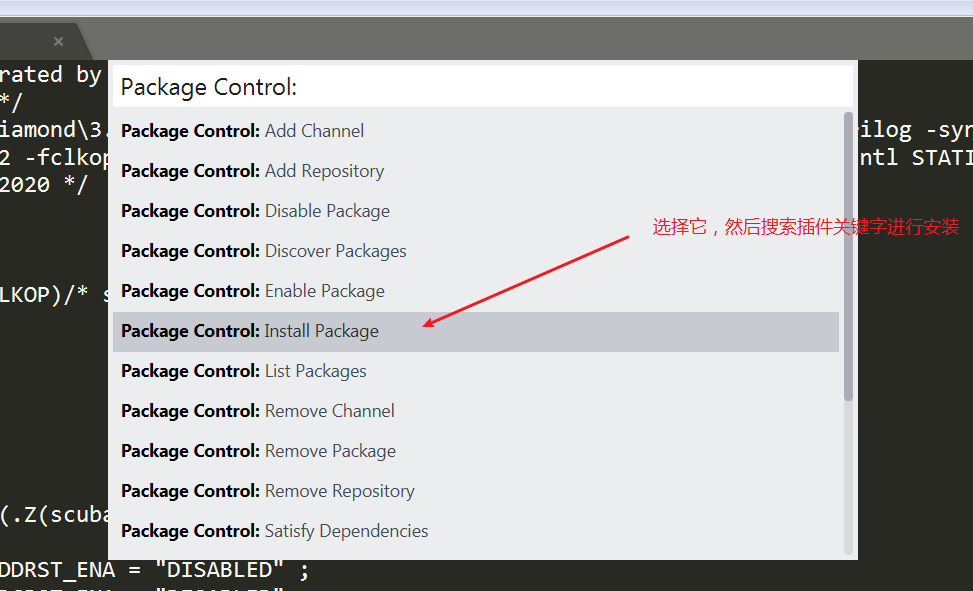

使用sublime text3支持各种语言的编辑,有时候需要安装相应的插件,而插件的安装需要使用包管理工具。

打开后有很多功能,我们最多的使用就是`install package`。

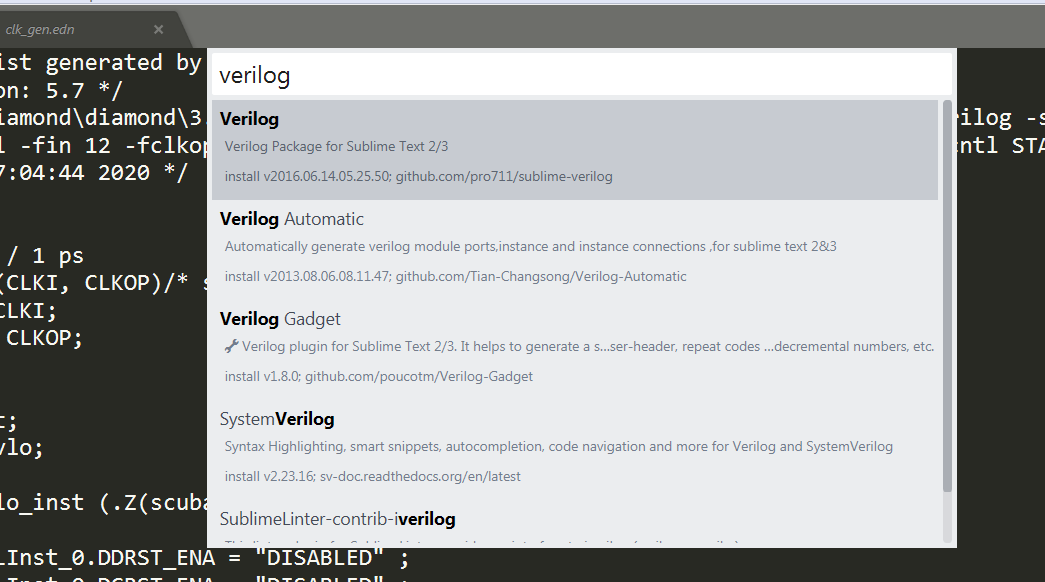

### 3、安装verilog支持

选择需要安装的插件,点击即可进行安装。

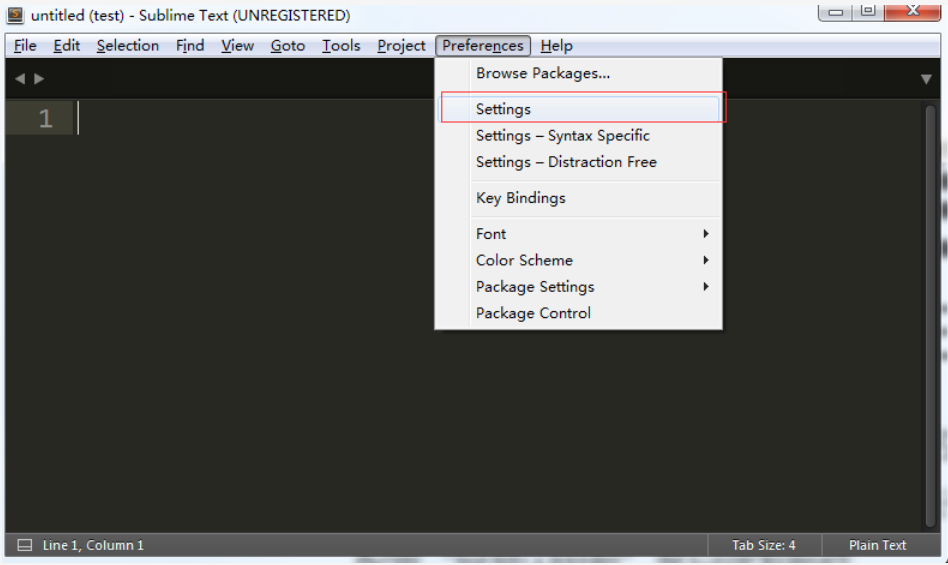

### 4、失焦自动化保存

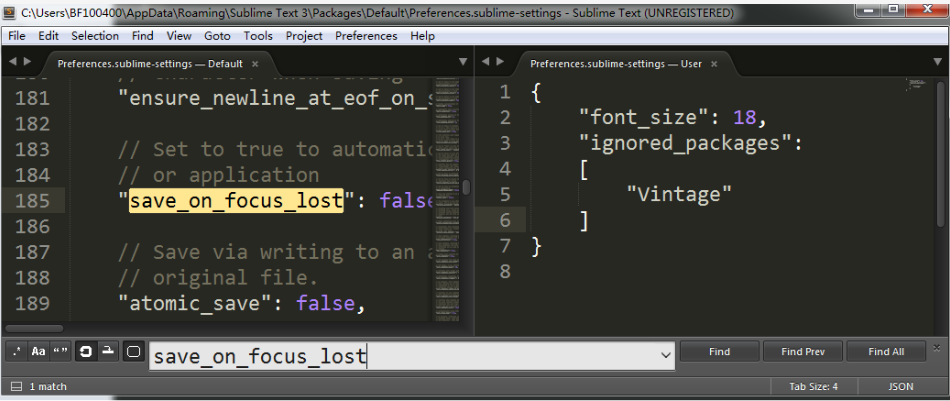

第一步:preferences 下面的settings;(和老版本的不一样了吧,之前有什么default 和 users,这里只有settings)

第二步:现在分两边了,左边是只读的不能编辑,在左边ctrl + f ,然后在下面输入框里输入save_on_focus_lost,或者找185行

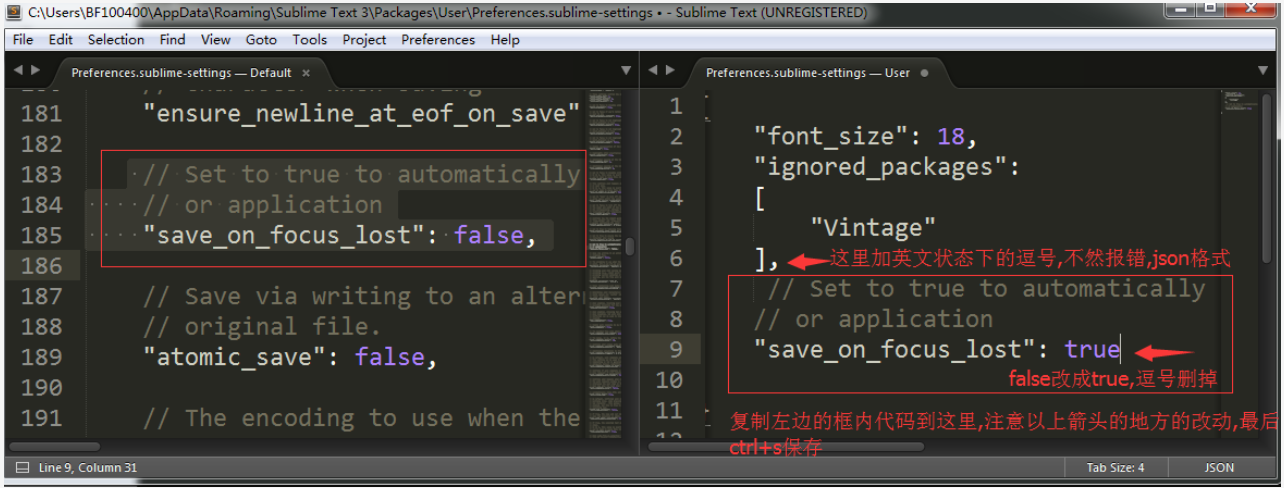

第三部:看下图就搞定了,复制这段代码到右边的框里,然后把false ,改成true 把true后面的逗号删掉,上面的一段代码结束加英文状态下的逗号就好,今后就不用ctrl+s了,舒心多了!

### 5、安装和配置ctags

此部分转载说明

```

作者:Wallys

链接:https://www.jianshu.com/p/543d9e894177

来源:简书

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

```

***第一步:在 ST3 安装 CTags 插件***

1. 在 ST3 快捷键 Crtl+Shift+P 然后输入 pci ,选择“ Package Control: Install Package ”启动安装插件程序;

2. 启动安装程序后,在命令行输入 ctags ,选择 CTags 插件并回车,等待插件安装完毕;

***第二步:下载最新的 ctags 文件***

1. 前往 http://ctags.sourceforge.net/ 下载,最新版本为09年发布的5.8版本;

2. 下载后将压缩包解压到非中文目录下,例如 E:\\SublimeText\\ctags58 ;

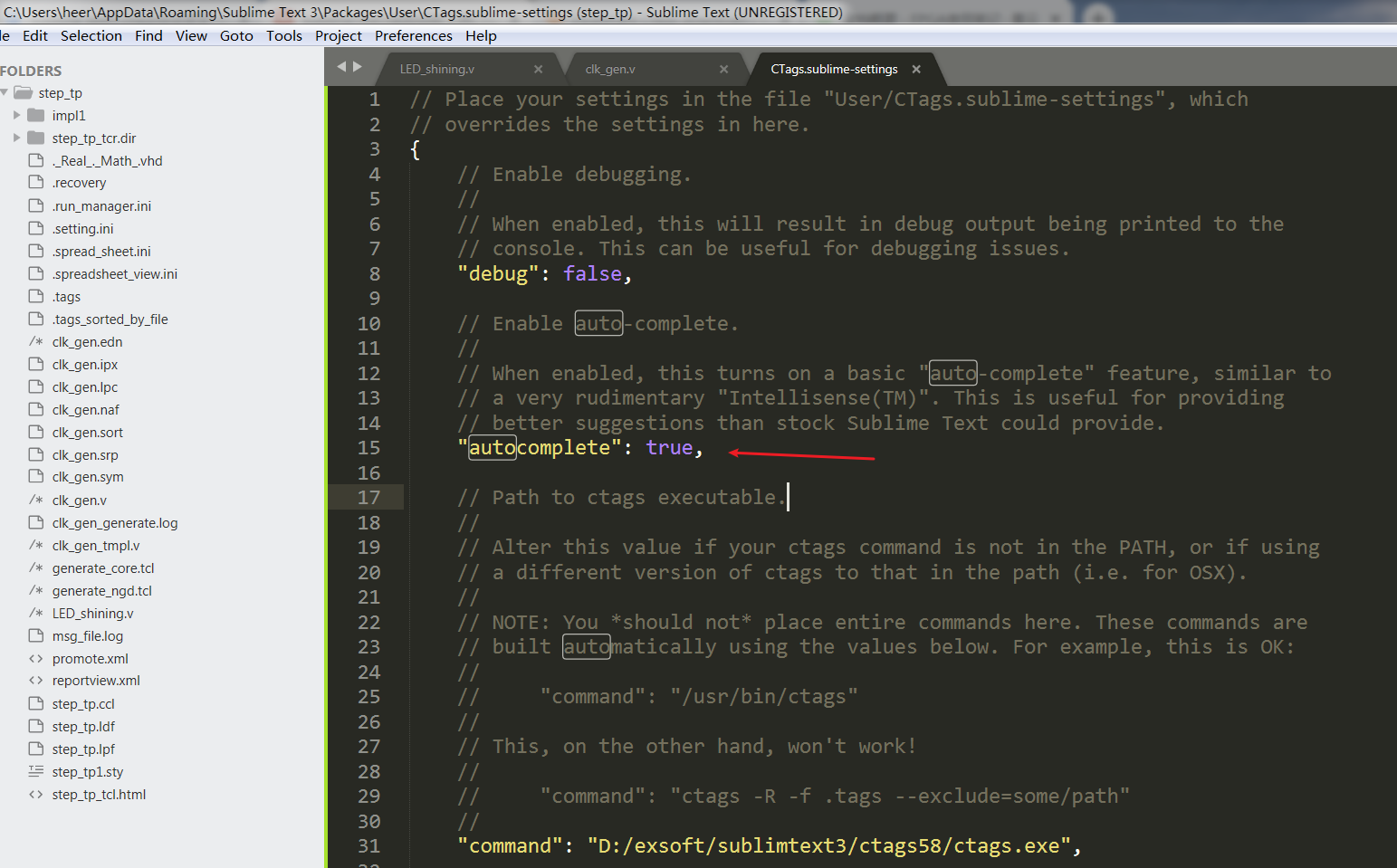

***第三步:配置 ctags 路径***

1. 在 ST3 打开 Preferences -> Package Setting -> CTags -> Setting-Default ,并复制全部代码,然后粘贴到 Setting-User 中;

2. 在 Setting-User 中找到 “command” ,在后面添加 ctags.exe 的路径【"command": "E:/SublimeText/ctags58/ctags.exe",】 ;

***第四步:配置使用操作习惯***

1. 配置目标:利用 **Ctrl+鼠标按钮** 的操作实现函数追踪;

2. 在 ST3 打开 Preferences -> Package Setting -> CTags -> Mouse Bindings-Default ,并复制全部代码,然后粘贴到 Mouse Bindings-User 中;

3. 修改 modifiers 的参数,去掉 shift ,然后保存(如果有其他习惯,可以把 modifiers 参数设置为其他键盘按键,只要不与其他热键冲突即可);

4. 当然还可以配置修改后自动重新生成tags文件,修改usr setting即可!

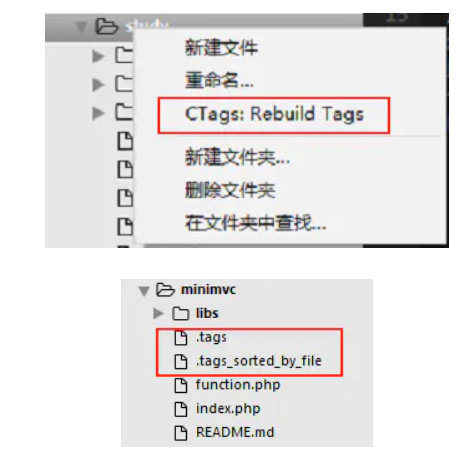

***第五步:生成 .tags 文件***

在项目文件夹管理器中,找到项目文件夹,右键点击 CTags:Rebuilding Tags ,文件夹中会生成 .tags 和 .tags_sorted_by_files 两个文件;

***第六步:使用追踪功能***

在项目中,可以在函数名上,按**Ctrl+鼠标左键**快速定位到函数体;在函数体按 Ctrl+鼠标右键 返回原文件。

上述方法可以实现verilog代码的跳转。

### 6、配置字体

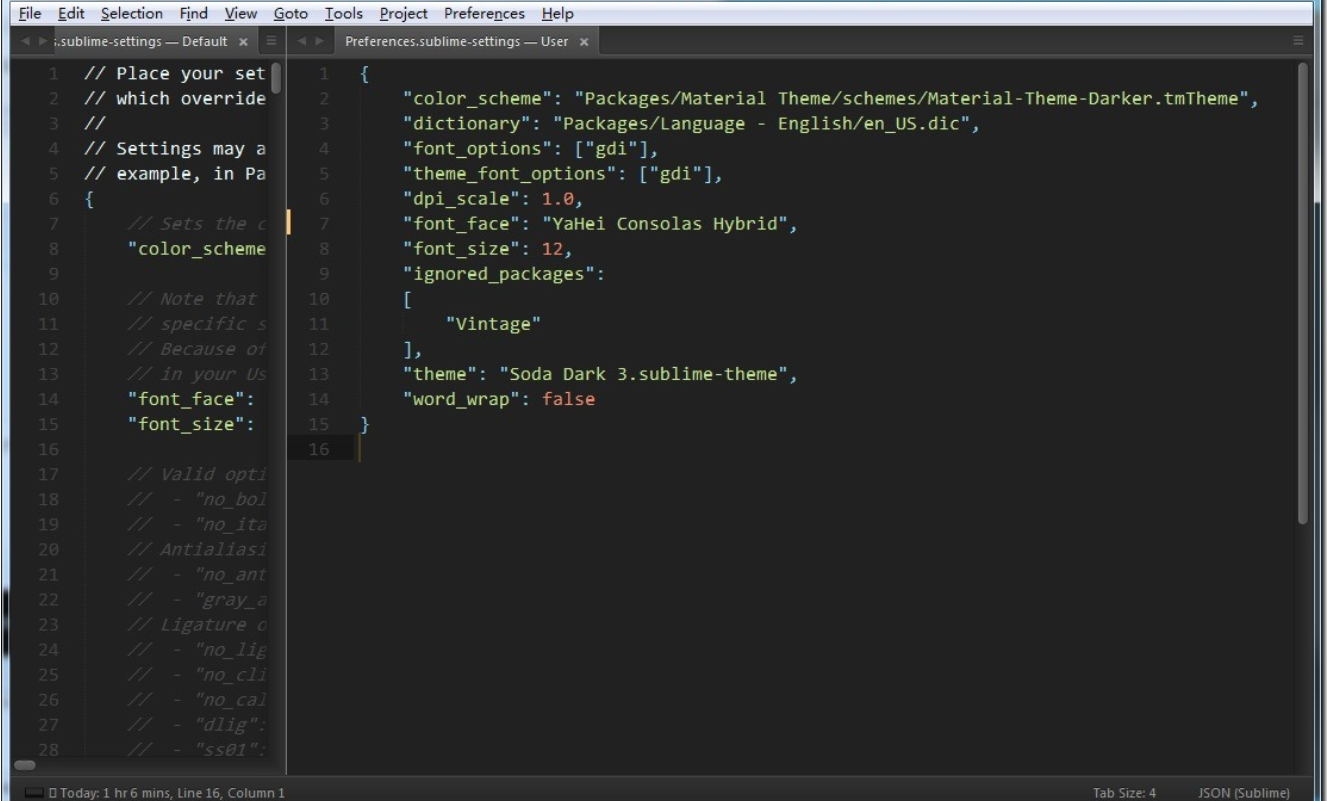

首选需要在本机安装漂亮的字体,我们选用的是YaHei Consolas Hybrid,是英文Consolas与中文微软雅黑的结合字体,把字体下载并安装到本地计算机,然后就要打开Sublime Text 3进行设置,设置方法:

```

菜单Preferences->Settings

```

然后在User部分看到类似以下格式的内容:

```

{

"color_scheme": "Packages/Material Theme/schemes/Material-Theme-Darker.tmTheme",

"dictionary": "Packages/Language - English/en_US.dic",

"ignored_packages":

[

"Vintage"

],

"theme": "Soda Dark 3.sublime-theme",

"word_wrap": false

}

```

我们在其中添加以下代码:

```

"font_options": ["gdi"],

"theme_font_options": ["gdi"],

"dpi_scale": 1.0,

"font_face": "YaHei Consolas Hybrid",

"font_size": 12,

```

然后Ctrl+S保存,如果输入无误,而且计算机中确认安装有YaHei Consolas Hybrid这个字体,那么设置就会立即生效

效果如下:

- 序

- 第1章 Linux下开发FPGA

- 1.1 Linux下安装diamond

- 1.2 使用轻量级linux仿真工具iverilog

- 1.3 使用linux shell来读写串口

- 1.4 嵌入式上的linux

- 设备数教程

- linux C 标准库文档

- linux 网络编程

- 开机启动流程

- 1.5 linux上实现与树莓派,FPGA等通信的串口脚本

- 第2章 Intel FPGA的使用

- 2.1 特别注意

- 2.2 高级应用开发流程

- 2.2.1 生成二进制bit流rbf

- 2.2.2 制作Preloader Image

- 2.2.2.1 生成BSP文件

- 2.2.2.2 编译preloader和uboot

- 2.2.2.3 更新SD的preloader和uboot

- 2.3 HPS使用

- 2.3.1 通过JTAG下载代码

- 2.3.2 HPS软件部分开发

- 2.3 quartus中IP核的使用

- 2.3.1 Intel中RS232串口IP的使用

- 2.4 一些问题的解决方法

- 2.4.1 关于引脚的复用的综合出错

- 第3章 关于C/C++的一些语法

- 3.1 C中数组作为形参不传长度

- 3.2 汇编中JUMP和CALL的区别

- 3.3 c++中map的使用

- 3.4 链表的一些应用

- 3.5 vector的使用

- 3.6 使用C实现一个简单的FIFO

- 3.6.1 循环队列

- 3.7 C语言不定长参数

- 3.8 AD采样计算同频信号的相位差

- 3.9 使用C实现栈

- 3.10 增量式PID

- 第4章 Xilinx的FPGA使用

- 4.1 Alinx使用中的一些问题及解决方法

- 4.1.1 在Genarate Bitstream时提示没有name.tcl

- 4.1.2 利用verilog求位宽

- 4.1.3 vivado中AXI写DDR说明

- 4.1.4 zynq中AXI GPIO中断问题

- 4.1.5 关于时序约束

- 4.1.6 zynq的PS端利用串口接收电脑的数据

- 4.1.7 SDK启动出错的解决方法

- 4.1.8 让工具综合是不优化某一模块的方法

- 4.1.9 固化程序(双核)

- 4.1.10 分配引脚时的问题

- 4.1.11 vivado仿真时相对文件路径的问题

- 4.2 GCC使用Attribute分配空间给变量

- 4.3 关于Zynq的DDR写入byte和word的方法

- 4.4 常用模块

- 4.4.1 I2S接收串转并

- 4.5 时钟约束

- 4.5.1 时钟约束

- 4.6 VIVADO使用

- 4.6.1 使用vivado进行仿真

- 4.7 关于PicoBlaze软核的使用

- 4.8 vivado一些IP的使用

- 4.8.1 float-point浮点单元的使用

- 4.10 zynq的双核中断

- 第5章 FPGA的那些好用的工具

- 5.1 iverilog

- 5.2 Arduino串口绘图器工具

- 5.3 LabVIEW

- 5.4 FPGA开发实用小工具

- 5.5 Linux下绘制时序图软件

- 5.6 verilog和VHDL相互转换工具

- 5.7 linux下搭建轻量易用的verilog仿真环境

- 5.8 VCS仿真verilog并查看波形

- 5.9 Verilog开源的综合工具-Yosys

- 5.10 sublim text3编辑器配置verilog编辑环境

- 5.11 在线工具

- 真值表 -> 逻辑表达式

- 5.12 Modelsim使用命令仿真

- 5.13 使用TCL实现的个人仿真脚本

- 5.14 在cygwin下使用命令行下载arduino代码到开发板

- 5.15 STM32开发

- 5.15.1 安装Atollic TrueSTUDIO for STM32

- 5.15.2 LED闪烁吧

- 5.15.3 模拟U盘

- 第6章 底层实现

- 6.1 硬件实现加法的流程

- 6.2 硬件实现乘法器

- 6.3 UART实现

- 6.3.1 通用串口发送模块

- 6.4 二进制数转BCD码

- 6.5 基本开源资源

- 6.5.1 深度资源

- 6.5.2 FreeCore资源集合

- 第7章 常用模块

- 7.1 温湿度传感器DHT11的verilog驱动

- 7.2 DAC7631驱动(verilog)

- 7.3 按键消抖

- 7.4 小脚丫数码管显示

- 7.5 verilog实现任意人数表决器

- 7.6 基本模块head.v

- 7.7 四相八拍步进电机驱动

- 7.8 单片机部分

- 7.8.1 I2C OLED驱动

- 第8章 verilog 扫盲区

- 8.1 时序电路中数据的读写

- 8.2 从RTL角度来看verilog中=和<=的区别

- 8.3 case和casez的区别

- 8.4 关于参数的传递与读取(paramter)

- 8.5 关于符号优先级

- 第9章 verilog中的一些语法使用

- 9.1 可综合的repeat

- 第10章 system verilog

- 10.1 简介

- 10.2 推荐demo学习网址

- 10.3 VCS在linux上环境的搭建

- 10.4 deepin15.11(linux)下搭建system verilog的vcs仿真环境

- 10.5 linux上使用vcs写的脚本仿真管理

- 10.6 system verilog基本语法

- 10.6.1 数据类型

- 10.6.2 枚举与字符串

- 第11章 tcl/tk的使用

- 11.1 使用Tcl/Tk

- 11.2 tcl基本语法教程

- 11.3 Tk的基本语法

- 11.3.1 建立按钮

- 11.3.2 复选框

- 11.3.3 单选框

- 11.3.4 标签

- 11.3.5 建立信息

- 11.3.6 建立输入框

- 11.3.7 旋转框

- 11.3.8 框架

- 11.3.9 标签框架

- 11.3.10 将窗口小部件分配到框架/标签框架

- 11.3.11 建立新的上层窗口

- 11.3.12 建立菜单

- 11.3.13 上层窗口建立菜单

- 11.3.14 建立滚动条

- 11.4 窗口管理器

- 11.5 一些学习的脚本

- 11.6 一些常用的操作语法实现

- 11.6.1 删除同一后缀的文件

- 11.7 在Lattice的Diamond中使用tcl

- 第12章 FPGA的重要知识

- 12.1 面积与速度的平衡与互换

- 12.2 硬件原则

- 12.3 系统原则

- 12.4 同步设计原则

- 12.5 乒乓操作

- 12.6 串并转换设计技巧

- 12.7 流水线操作设计思想

- 12.8 数据接口的同步方法

- 第13章 小项目

- 13.1 数字滤波器

- 13.2 FIFO

- 13.3 一个精简的CPU( mini-mcu )

- 13.3.1 基本功能实现

- 13.3.2 中断添加

- 13.3.3 使用中断实现流水灯(实际硬件验证)

- 13.3.4 综合一点的应用示例

- 13.4.5 使用flex开发汇编编译器

- 13.4.5 linux--Flex and Bison

- 13.4 有符号数转单精度浮点数

- 13.5 串口调试FPGA模板