[TOC]

## 介绍

Yosys是Verilog RTL综合的框架。它目前具有广泛的Verilog-2005支持,并为各种应用程序领域提供了一组基本的综合算法。所选功能和典型应用:

* 处理几乎所有可综合的Verilog-2005设计

* 将Verilog转换为BLIF / EDIF / BTOR / SMT-LIB /简单的RTL Verilog /等等

* 内置的形式检查属性和等效性的方法

* 映射到ASIC标准单元库(自由文件格式)

* 映射到Xilinx 7系列和Lattice iCE40 FPGA

* 自定义流程的基础和/或前端

通过使用合成脚本组合现有过程(算法)并根据需要通过扩展Yosys C ++代码库添加其他过程,可以使Yosys适于执行任何综合工作。 <br/>

Yosys是根据ISC许可(与MIT许可或2子BSD许可类似的GPL兼容许可)许可的免费软件。<br/>

事实上,yosys是一个解释器,就如同python的解释器一样,于是从理论上我们可以在linux使用sheban来写脚本运行!

[文档推荐]([https://www.kutu66.com/GitHub/article\_94386](https://www.kutu66.com/GitHub/article_94386))

## 在deepin上的安装

**首先安装所需要的依赖项目**

```bash

sudo apt-get install build-essential clang bison flex \

libreadline-dev gawk tcl-dev libffi-dev git \

graphviz xdot pkg-config python3 libboost-system-dev \

libboost-python-dev libboost-filesystem-dev zlib1g-dev

```

**安装yosys**

使用一下命令进行安装

```bash

sudo apt-get install yosys

```

## 关于帮助

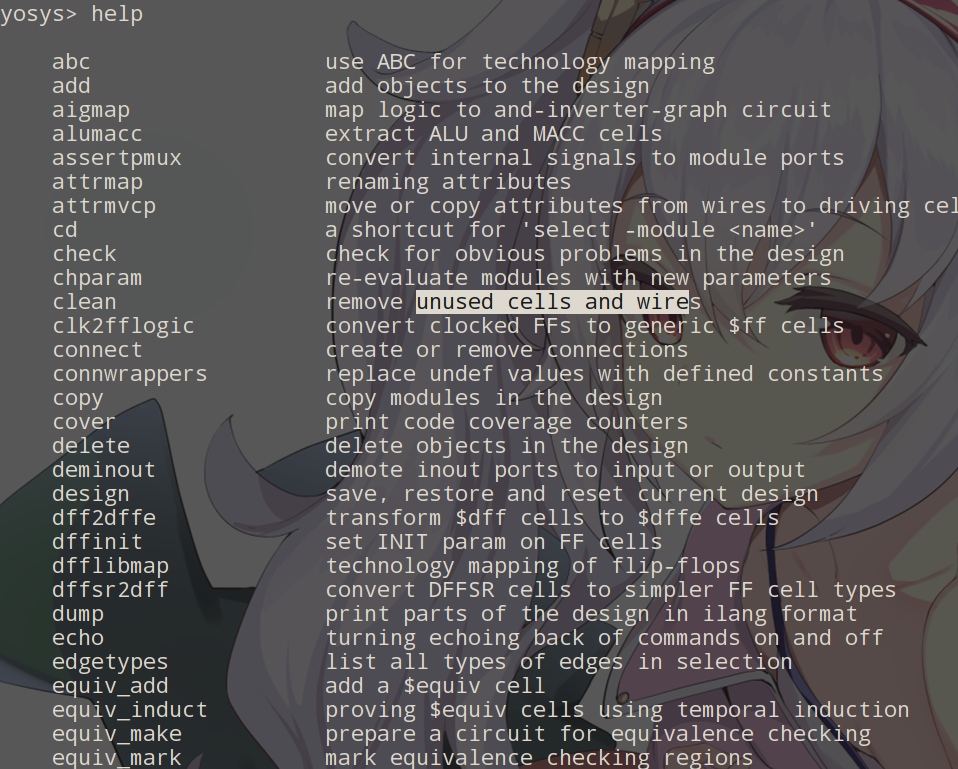

对于不同版本的yosys,有些命令可能不同,yosys是一个解释器,可以在终端输入`yosys`进入,然后输入`help`查看支持的命令!

## 分步说明一个简单的例子

**新建`foo.v`文件,文件内容如下所示**

```

module foo (

input a,

input b,

input c,

output o

);

assign o = (a & b) | c;

endmodule

```

**终端切换到yosys解释器,终端输入yosys即可**

```

yosys

```

**读入待分析的verilog文件**

当然根据版本的不同可能read要换成 read_verilog.

```

yosys> read -sv foo.v

1. Executing Verilog-2005 frontend.

Parsing SystemVerilog input from `foo.v' to AST representation.

Generating RTLIL representation for module `\foo'.

Successfully finished Verilog frontend.

```

**指出顶层模块**

```

yosys> hierarchy -top foo

2. Executing HIERARCHY pass (managing design hierarchy).

2.1. Analyzing design hierarchy..

Top module: \foo

2.2. Analyzing design hierarchy..

Top module: \foo

Removed 0 unused modules.

```

**将设计以Yosys的内部格式写入控制台**

```

yosys> write_ilang

3. Executing ILANG backend.

Output filename: <stdout>

# Generated by Yosys 0.8 (git sha1 5706e90)

autoidx 3

attribute \top 1

attribute \src "foo.v:1"

module \foo

attribute \src "foo.v:8"

wire $and$foo.v:8$1_Y

attribute \src "foo.v:8"

wire $or$foo.v:8$2_Y

attribute \src "foo.v:2"

wire input 1 \a

attribute \src "foo.v:3"

wire input 2 \b

attribute \src "foo.v:4"

wire input 3 \c

attribute \src "foo.v:5"

wire output 4 \o

attribute \src "foo.v:8"

cell $and $and$foo.v:8$1

parameter \A_SIGNED 0

parameter \A_WIDTH 1

parameter \B_SIGNED 0

parameter \B_WIDTH 1

parameter \Y_WIDTH 1

connect \A \a

connect \B \b

connect \Y $and$foo.v:8$1_Y

end

attribute \src "foo.v:8"

cell $or $or$foo.v:8$2

parameter \A_SIGNED 0

parameter \A_WIDTH 1

parameter \B_SIGNED 0

parameter \B_WIDTH 1

parameter \Y_WIDTH 1

connect \A $and$foo.v:8$1_Y

connect \B \c

connect \Y $or$foo.v:8$2_Y

end

connect \o $or$foo.v:8$2_Y

end

```

**将流程(always块)转换为网表元素并执行一些简单的优化**

```

yosys> proc; opt

4. Executing PROC pass (convert processes to netlists).

4.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

4.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

Removed a total of 0 dead cases.

4.3. Executing PROC_INIT pass (extract init attributes).

4.4. Executing PROC_ARST pass (detect async resets in processes).

4.5. Executing PROC_MUX pass (convert decision trees to multiplexers).

4.6. Executing PROC_DLATCH pass (convert process syncs to latches).

4.7. Executing PROC_DFF pass (convert process syncs to FFs).

4.8. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

5. Executing OPT pass (performing simple optimizations).

5.1. Executing OPT_EXPR pass (perform const folding).

5.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\foo'.

Removed a total of 0 cells.

5.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \foo..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

5.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \foo.

Performed a total of 0 changes.

5.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\foo'.

Removed a total of 0 cells.

5.6. Executing OPT_RMDFF pass (remove dff with constant values).

5.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \foo..

removed 1 unused temporary wires.

Removed 0 unused cells and 1 unused wires.

5.8. Executing OPT_EXPR pass (perform const folding).

5.9. Finished OPT passes. (There is nothing left to do.)

```

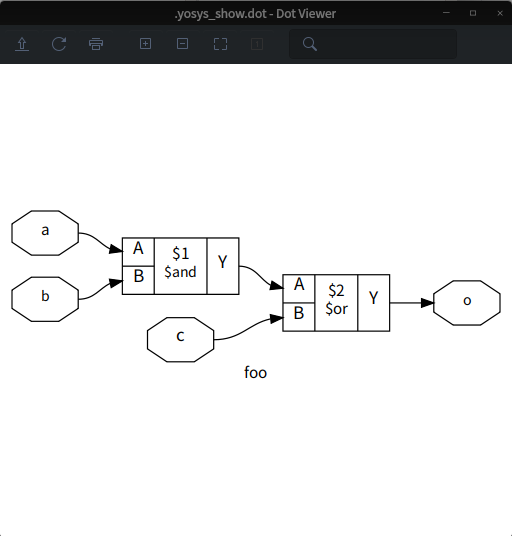

**使用xdot显示设计网表**

```

yosys> show

```

显示结果如下:

同样的实现,使用gv可用以下命令实现:

```

yosys> show -format ps -viewer gv

```

**将网表转换为门逻辑并执行一些简单的优化**

```

yosys> techmap; opt

7. Executing TECHMAP pass (map to technology primitives).

7.1. Executing Verilog-2005 frontend.

Parsing Verilog input from `<techmap.v>' to AST representation.

Generating RTLIL representation for module `\_90_simplemap_bool_ops'.

Generating RTLIL representation for module `\_90_simplemap_reduce_ops'.

Generating RTLIL representation for module `\_90_simplemap_logic_ops'.

Generating RTLIL representation for module `\_90_simplemap_compare_ops'.

Generating RTLIL representation for module `\_90_simplemap_various'.

Generating RTLIL representation for module `\_90_simplemap_registers'.

Generating RTLIL representation for module `\_90_shift_ops_shr_shl_sshl_sshr'.

Generating RTLIL representation for module `\_90_shift_shiftx'.

Generating RTLIL representation for module `\_90_fa'.

Generating RTLIL representation for module `\_90_lcu'.

Generating RTLIL representation for module `\_90_alu'.

Generating RTLIL representation for module `\_90_macc'.

Generating RTLIL representation for module `\_90_alumacc'.

Generating RTLIL representation for module `\$__div_mod_u'.

Generating RTLIL representation for module `\$__div_mod'.

Generating RTLIL representation for module `\_90_div'.

Generating RTLIL representation for module `\_90_mod'.

Generating RTLIL representation for module `\_90_pow'.

Generating RTLIL representation for module `\_90_pmux'.

Generating RTLIL representation for module `\_90_lut'.

Successfully finished Verilog frontend.

Mapping foo.$and$foo.v:8$1 ($and) with simplemap.

Mapping foo.$or$foo.v:8$2 ($or) with simplemap.

No more expansions possible.

8. Executing OPT pass (performing simple optimizations).

8.1. Executing OPT_EXPR pass (perform const folding).

8.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\foo'.

Removed a total of 0 cells.

8.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \foo..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

8.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \foo.

Performed a total of 0 changes.

8.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\foo'.

Removed a total of 0 cells.

8.6. Executing OPT_RMDFF pass (remove dff with constant values).

8.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \foo..

Removed 0 unused cells and 1 unused wires.

8.8. Executing OPT_EXPR pass (perform const folding).

8.9. Finished OPT passes. (There is nothing left to do.)

```

**将设计网表写入新的Verilog文件**

```

yosys> write_verilog synth.v

```

这样流程基本就结束了!

## 脚本方式执行

If ABC is enabled in the Yosys build configuration and a cell library is given in the liberty file `mycells.lib`, the following synthesis script will synthesize for the given cell library:

```

# read design

read -sv foo.v

hierarchy -top foo

# the high-level stuff

proc; fsm; opt; memory; opt

# mapping to internal cell library

techmap; opt

# mapping flip-flops to mycells.lib

dfflibmap -liberty mycells.lib

# mapping logic to mycells.lib

abc -liberty mycells.lib

# cleanup

clean

```

## 简单脚本实现

建立foo.ys文件,内容如下:

```

#!/usr/bin/env yosys

read -sv foo.v

hierarchy -top foo

proc; opt; techmap; opt

show

write_verilog synth.v

```

执行脚本可以使用 `yosys foo.ys`执行。<br/>

前面已经说到yosys是一个解释器,那么我们可以为foo.ys添加执行权限,使用`chmod +x foo.ys`,然后就如同在linux上执行bash脚本一样,使用 `./foo.ys`来执行。

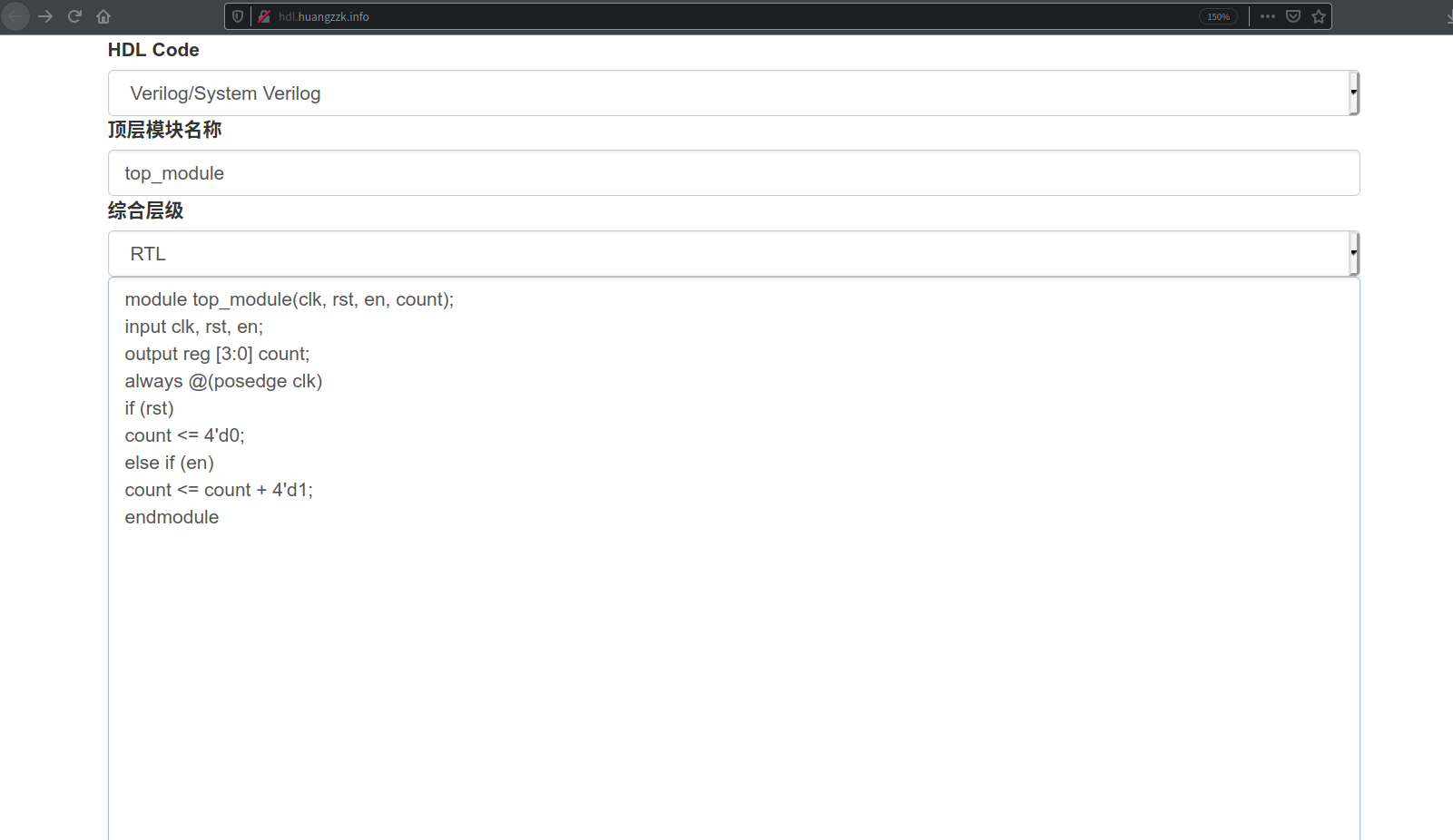

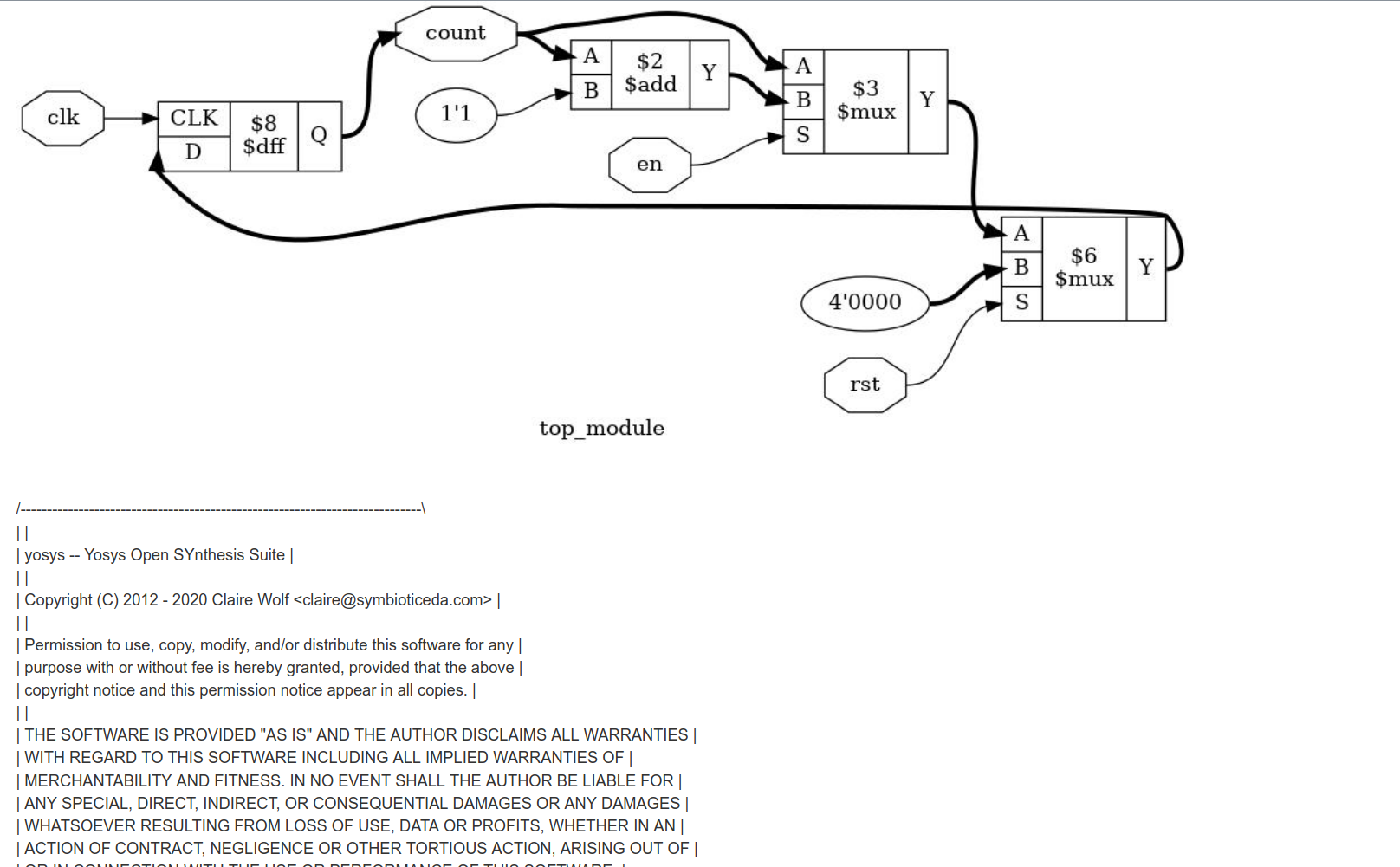

## yosys的web版本

我们有时候学习就只想很快的查看一些RTL或者GATE级的结果,安装环境可能遇到各种问题,在这种情况下,我们可以使用yosys的web版本,链接地址:

[yosys的web版本](http://hdl.huangzzk.info/)

## 链接地址

[yosys github地址](https://github.com/YosysHQ/yosys)

[测试源码地址](https://gitee.com/yuan_hp/yosys-test)

- 序

- 第1章 Linux下开发FPGA

- 1.1 Linux下安装diamond

- 1.2 使用轻量级linux仿真工具iverilog

- 1.3 使用linux shell来读写串口

- 1.4 嵌入式上的linux

- 设备数教程

- linux C 标准库文档

- linux 网络编程

- 开机启动流程

- 1.5 linux上实现与树莓派,FPGA等通信的串口脚本

- 第2章 Intel FPGA的使用

- 2.1 特别注意

- 2.2 高级应用开发流程

- 2.2.1 生成二进制bit流rbf

- 2.2.2 制作Preloader Image

- 2.2.2.1 生成BSP文件

- 2.2.2.2 编译preloader和uboot

- 2.2.2.3 更新SD的preloader和uboot

- 2.3 HPS使用

- 2.3.1 通过JTAG下载代码

- 2.3.2 HPS软件部分开发

- 2.3 quartus中IP核的使用

- 2.3.1 Intel中RS232串口IP的使用

- 2.4 一些问题的解决方法

- 2.4.1 关于引脚的复用的综合出错

- 第3章 关于C/C++的一些语法

- 3.1 C中数组作为形参不传长度

- 3.2 汇编中JUMP和CALL的区别

- 3.3 c++中map的使用

- 3.4 链表的一些应用

- 3.5 vector的使用

- 3.6 使用C实现一个简单的FIFO

- 3.6.1 循环队列

- 3.7 C语言不定长参数

- 3.8 AD采样计算同频信号的相位差

- 3.9 使用C实现栈

- 3.10 增量式PID

- 第4章 Xilinx的FPGA使用

- 4.1 Alinx使用中的一些问题及解决方法

- 4.1.1 在Genarate Bitstream时提示没有name.tcl

- 4.1.2 利用verilog求位宽

- 4.1.3 vivado中AXI写DDR说明

- 4.1.4 zynq中AXI GPIO中断问题

- 4.1.5 关于时序约束

- 4.1.6 zynq的PS端利用串口接收电脑的数据

- 4.1.7 SDK启动出错的解决方法

- 4.1.8 让工具综合是不优化某一模块的方法

- 4.1.9 固化程序(双核)

- 4.1.10 分配引脚时的问题

- 4.1.11 vivado仿真时相对文件路径的问题

- 4.2 GCC使用Attribute分配空间给变量

- 4.3 关于Zynq的DDR写入byte和word的方法

- 4.4 常用模块

- 4.4.1 I2S接收串转并

- 4.5 时钟约束

- 4.5.1 时钟约束

- 4.6 VIVADO使用

- 4.6.1 使用vivado进行仿真

- 4.7 关于PicoBlaze软核的使用

- 4.8 vivado一些IP的使用

- 4.8.1 float-point浮点单元的使用

- 4.10 zynq的双核中断

- 第5章 FPGA的那些好用的工具

- 5.1 iverilog

- 5.2 Arduino串口绘图器工具

- 5.3 LabVIEW

- 5.4 FPGA开发实用小工具

- 5.5 Linux下绘制时序图软件

- 5.6 verilog和VHDL相互转换工具

- 5.7 linux下搭建轻量易用的verilog仿真环境

- 5.8 VCS仿真verilog并查看波形

- 5.9 Verilog开源的综合工具-Yosys

- 5.10 sublim text3编辑器配置verilog编辑环境

- 5.11 在线工具

- 真值表 -> 逻辑表达式

- 5.12 Modelsim使用命令仿真

- 5.13 使用TCL实现的个人仿真脚本

- 5.14 在cygwin下使用命令行下载arduino代码到开发板

- 5.15 STM32开发

- 5.15.1 安装Atollic TrueSTUDIO for STM32

- 5.15.2 LED闪烁吧

- 5.15.3 模拟U盘

- 第6章 底层实现

- 6.1 硬件实现加法的流程

- 6.2 硬件实现乘法器

- 6.3 UART实现

- 6.3.1 通用串口发送模块

- 6.4 二进制数转BCD码

- 6.5 基本开源资源

- 6.5.1 深度资源

- 6.5.2 FreeCore资源集合

- 第7章 常用模块

- 7.1 温湿度传感器DHT11的verilog驱动

- 7.2 DAC7631驱动(verilog)

- 7.3 按键消抖

- 7.4 小脚丫数码管显示

- 7.5 verilog实现任意人数表决器

- 7.6 基本模块head.v

- 7.7 四相八拍步进电机驱动

- 7.8 单片机部分

- 7.8.1 I2C OLED驱动

- 第8章 verilog 扫盲区

- 8.1 时序电路中数据的读写

- 8.2 从RTL角度来看verilog中=和<=的区别

- 8.3 case和casez的区别

- 8.4 关于参数的传递与读取(paramter)

- 8.5 关于符号优先级

- 第9章 verilog中的一些语法使用

- 9.1 可综合的repeat

- 第10章 system verilog

- 10.1 简介

- 10.2 推荐demo学习网址

- 10.3 VCS在linux上环境的搭建

- 10.4 deepin15.11(linux)下搭建system verilog的vcs仿真环境

- 10.5 linux上使用vcs写的脚本仿真管理

- 10.6 system verilog基本语法

- 10.6.1 数据类型

- 10.6.2 枚举与字符串

- 第11章 tcl/tk的使用

- 11.1 使用Tcl/Tk

- 11.2 tcl基本语法教程

- 11.3 Tk的基本语法

- 11.3.1 建立按钮

- 11.3.2 复选框

- 11.3.3 单选框

- 11.3.4 标签

- 11.3.5 建立信息

- 11.3.6 建立输入框

- 11.3.7 旋转框

- 11.3.8 框架

- 11.3.9 标签框架

- 11.3.10 将窗口小部件分配到框架/标签框架

- 11.3.11 建立新的上层窗口

- 11.3.12 建立菜单

- 11.3.13 上层窗口建立菜单

- 11.3.14 建立滚动条

- 11.4 窗口管理器

- 11.5 一些学习的脚本

- 11.6 一些常用的操作语法实现

- 11.6.1 删除同一后缀的文件

- 11.7 在Lattice的Diamond中使用tcl

- 第12章 FPGA的重要知识

- 12.1 面积与速度的平衡与互换

- 12.2 硬件原则

- 12.3 系统原则

- 12.4 同步设计原则

- 12.5 乒乓操作

- 12.6 串并转换设计技巧

- 12.7 流水线操作设计思想

- 12.8 数据接口的同步方法

- 第13章 小项目

- 13.1 数字滤波器

- 13.2 FIFO

- 13.3 一个精简的CPU( mini-mcu )

- 13.3.1 基本功能实现

- 13.3.2 中断添加

- 13.3.3 使用中断实现流水灯(实际硬件验证)

- 13.3.4 综合一点的应用示例

- 13.4.5 使用flex开发汇编编译器

- 13.4.5 linux--Flex and Bison

- 13.4 有符号数转单精度浮点数

- 13.5 串口调试FPGA模板