[TOC]

> # 说明

由于fpga的系统时钟可能会存在差异,之前搜索的一些串口模块都是要经过修改才能更好的适配当前的项目,为了之后可以更快的实现项目串口的添加,在这里首先写了一个**通用串口发送模块**,根据系统的时钟和需要的波特率,可自行设置。

> # 实现如下

```verilog

`timescale 1ns / 1ps

// ********************************************************************

// FileName : uart_tx.v

// Author :hpy

// Email :yuan_hp@qq.com

// Date :2020年12月06日

// Description :串口发送模块,该模块使用时必须先复位一次,否则无法工作

// 这是因为设计的时候使用了独热码,状态没有全零的。

// --------------------------------------------------------------------

/*-------------------------------------------

uart_tx #(

.CLK_FREQ(12000000), //时钟频率

.BSP(9600) // 波特率

) u1 (

.clk(clk),

.rst_n(),

.start() , // 发送触发标志,上升沿有效

.sdata(), //要发送的数据

.tx(), //串口tx

.busy(), //忙标志

.interrupt() //发送一个字节完毕的中断信号,数据发送完毕后会产生一个clk的上升沿脉冲

);

--------------------------------------------*/

module uart_tx#(

parameter CLK_FREQ = 12000000, //时钟频率

BSP = 9600 // 波特率

)(

input clk,

input rst_n,

input start , // 发送触发标志,上升沿有效

input [7:0]sdata, //要发送的数据

output reg tx,

output reg busy, //忙标志

output interrupt //中断信号

);

localparam CNT_MAX = CLK_FREQ / BSP; //根据时钟频率和波特率计算分频值

localparam CNT_HALF = (CNT_MAX>>1) ; //

//状态机状态

localparam

IDEL = 6'b000001,

PRE = 6'b000010,

START = 6'b000100,

TX_DATA = 6'b001000,

TX_CHECK = 6'b010000,

STOP = 6'b100000;

//assign busy = (nst != IDEL ) ;

always @(posedge clk) begin

if( !rst_n ) busy <= 1'b0;

else begin

if(start_p && (cst==IDEL))

busy <= 1'b1;

else if(nst == IDEL && bsp_clk)

busy <= 1'b0;

else busy <= busy;

end

end

reg [5:0] cst,nst;

/*****************************************************

* 产生数据接发送完毕的中断信号

*****************************************************/

reg busy_f;

assign interrupt = (~busy) & busy_f;

always@(posedge clk) begin

if( !rst_n ) begin

busy_f <= 1'b0;

end

else begin

busy_f <= busy;

end

end

function integer clog2 (input integer din);

for( clog2 = 0; din; clog2=clog2 +1)

din = din >>1;

endfunction

/*****************************************************

* 检测触发信号上升沿

*****************************************************/

reg start_f;

wire start_p;

assign start_p = start & (~start_f);

always@(posedge clk) begin

if ( !rst_n ) begin

start_f <= 1'b0;

//start_p <= 1'b0;

end else begin

start_f <= start;

//start_p <= start & (~start_f);

end

end

reg [ clog2(CNT_MAX) - 1 : 0 ] cnt ; //计数器

/*****************************************************

* 计数产生bps

*****************************************************/

wire bsp_clk;

assign bsp_clk = (cnt == CNT_HALF)? 1'B1 : 1'B0;

always@(posedge clk ) begin

if(!rst_n)begin

cnt <= 'd0;

end

else begin

if( cnt >= CNT_MAX - 1'b1 || ((cst == IDEL) && (start_p)))

cnt <= 1'b0;

else if(busy)

cnt <= cnt + 1'b1;

else cnt <= 'd0;

end

end

/*****************************************************

* 状态机到下一状态

*****************************************************/

always@(posedge clk) begin

if(rst_n == 1'b0 )begin

cst <= IDEL;

end else begin

if(cst == IDEL ) cst <= nst;

else

cst <= (bsp_clk) ? nst : cst;

end

end

/*****************************************************

* 状态机下一状态选择

*****************************************************/

reg [ 3 : 0 ] tx_cnt;

always@(*) begin

nst = IDEL;

case(cst)

IDEL : nst = (start_p)? PRE : IDEL;

PRE : nst = START;

START : nst = TX_DATA;

TX_DATA : nst = (tx_cnt >= 4'd8)? TX_CHECK : TX_DATA;

TX_CHECK :nst = STOP;

STOP: nst = IDEL;

default:nst = IDEL;

endcase

end

/*****************************************************

* 状态机输出

*****************************************************/

reg [7:0]tx_buf;

always@(posedge clk) begin

if(rst_n == 1'b0 )begin

tx <= 1'b1;

tx_cnt <= 4'd0;

end

else begin

case(nst)

IDEL: begin

tx <= 1'b1;

end

PRE: begin //由于时钟的原因,计算得到的分频值可能是小数,因此每次发数据之前都回复初始状态,不让误差累积,等一拍可实现

tx <= 1'b1;

tx_buf <= sdata;

end

START: if(bsp_clk) begin

tx <= 1'b0;

//tx_buf <= sdata;

tx_cnt <= 4'd0 ;

end

TX_DATA: if(bsp_clk) begin

tx_cnt <= tx_cnt + 1'b1;

tx <= tx_buf[0];

tx_buf <= tx_buf >> 1 ;

end

TX_CHECK : if(bsp_clk)begin //奇偶校验

tx <= 1'b1;

tx_cnt <= 4'b0;

end

STOP: if(bsp_clk) begin //停止位

tx <= 1'b1;

end

default: tx <= 1'b1;

endcase

end

end

endmodule

```

> # 使用示例

```verilog

module top

(

input clk, //输入系统12MHz时钟

output tx

);

wire tflag;

wire rst_n;

//产生复位信号

Rst_sys #(

.N(9000000) // 计数器最大值 ,取值要大于2

) rst_u1(

.clk(clk),

.rst_n(rst_n)

);

divide #(

.N(12000000)

) u2 (

.clk(clk),

.rst_n(rst_n),

.clkout(tflag)

);

reg [7:0] tx_data;

wire tx_inte;

always@(posedge clk) begin

if(rst_n == 0) begin

tx_data <=0;

start <= 1'b0;

end

else if(!tx_busy && (start==1'b0))begin

tx_data <= tx_data + 1;

start <= 1'b1;

end

else begin

start <= 1'b0;

end

end

wire tx_busy;

reg start;

uart_tx #(

.CLK_FREQ(12000000), //时钟频率

.BSP(9600) // 波特率

) u1 (

.clk(clk),

.rst_n(rst_n),

.start(start) , // 发送触发标志,上升沿有效

.sdata(tx_data), //要发送的数据

.tx(tx), //串口tx

.interrupt(tx_inte),

.busy(tx_busy) //忙标志

);

endmodule

```

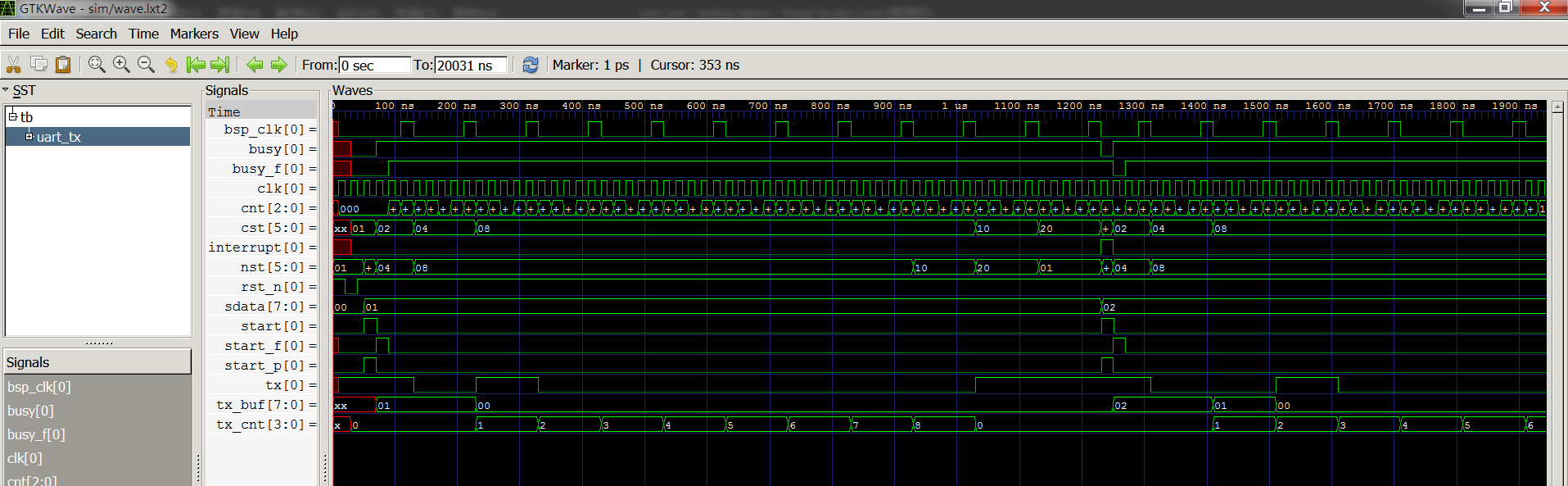

> # 仿真波形

- 序

- 第1章 Linux下开发FPGA

- 1.1 Linux下安装diamond

- 1.2 使用轻量级linux仿真工具iverilog

- 1.3 使用linux shell来读写串口

- 1.4 嵌入式上的linux

- 设备数教程

- linux C 标准库文档

- linux 网络编程

- 开机启动流程

- 1.5 linux上实现与树莓派,FPGA等通信的串口脚本

- 第2章 Intel FPGA的使用

- 2.1 特别注意

- 2.2 高级应用开发流程

- 2.2.1 生成二进制bit流rbf

- 2.2.2 制作Preloader Image

- 2.2.2.1 生成BSP文件

- 2.2.2.2 编译preloader和uboot

- 2.2.2.3 更新SD的preloader和uboot

- 2.3 HPS使用

- 2.3.1 通过JTAG下载代码

- 2.3.2 HPS软件部分开发

- 2.3 quartus中IP核的使用

- 2.3.1 Intel中RS232串口IP的使用

- 2.4 一些问题的解决方法

- 2.4.1 关于引脚的复用的综合出错

- 第3章 关于C/C++的一些语法

- 3.1 C中数组作为形参不传长度

- 3.2 汇编中JUMP和CALL的区别

- 3.3 c++中map的使用

- 3.4 链表的一些应用

- 3.5 vector的使用

- 3.6 使用C实现一个简单的FIFO

- 3.6.1 循环队列

- 3.7 C语言不定长参数

- 3.8 AD采样计算同频信号的相位差

- 3.9 使用C实现栈

- 3.10 增量式PID

- 第4章 Xilinx的FPGA使用

- 4.1 Alinx使用中的一些问题及解决方法

- 4.1.1 在Genarate Bitstream时提示没有name.tcl

- 4.1.2 利用verilog求位宽

- 4.1.3 vivado中AXI写DDR说明

- 4.1.4 zynq中AXI GPIO中断问题

- 4.1.5 关于时序约束

- 4.1.6 zynq的PS端利用串口接收电脑的数据

- 4.1.7 SDK启动出错的解决方法

- 4.1.8 让工具综合是不优化某一模块的方法

- 4.1.9 固化程序(双核)

- 4.1.10 分配引脚时的问题

- 4.1.11 vivado仿真时相对文件路径的问题

- 4.2 GCC使用Attribute分配空间给变量

- 4.3 关于Zynq的DDR写入byte和word的方法

- 4.4 常用模块

- 4.4.1 I2S接收串转并

- 4.5 时钟约束

- 4.5.1 时钟约束

- 4.6 VIVADO使用

- 4.6.1 使用vivado进行仿真

- 4.7 关于PicoBlaze软核的使用

- 4.8 vivado一些IP的使用

- 4.8.1 float-point浮点单元的使用

- 4.10 zynq的双核中断

- 第5章 FPGA的那些好用的工具

- 5.1 iverilog

- 5.2 Arduino串口绘图器工具

- 5.3 LabVIEW

- 5.4 FPGA开发实用小工具

- 5.5 Linux下绘制时序图软件

- 5.6 verilog和VHDL相互转换工具

- 5.7 linux下搭建轻量易用的verilog仿真环境

- 5.8 VCS仿真verilog并查看波形

- 5.9 Verilog开源的综合工具-Yosys

- 5.10 sublim text3编辑器配置verilog编辑环境

- 5.11 在线工具

- 真值表 -> 逻辑表达式

- 5.12 Modelsim使用命令仿真

- 5.13 使用TCL实现的个人仿真脚本

- 5.14 在cygwin下使用命令行下载arduino代码到开发板

- 5.15 STM32开发

- 5.15.1 安装Atollic TrueSTUDIO for STM32

- 5.15.2 LED闪烁吧

- 5.15.3 模拟U盘

- 第6章 底层实现

- 6.1 硬件实现加法的流程

- 6.2 硬件实现乘法器

- 6.3 UART实现

- 6.3.1 通用串口发送模块

- 6.4 二进制数转BCD码

- 6.5 基本开源资源

- 6.5.1 深度资源

- 6.5.2 FreeCore资源集合

- 第7章 常用模块

- 7.1 温湿度传感器DHT11的verilog驱动

- 7.2 DAC7631驱动(verilog)

- 7.3 按键消抖

- 7.4 小脚丫数码管显示

- 7.5 verilog实现任意人数表决器

- 7.6 基本模块head.v

- 7.7 四相八拍步进电机驱动

- 7.8 单片机部分

- 7.8.1 I2C OLED驱动

- 第8章 verilog 扫盲区

- 8.1 时序电路中数据的读写

- 8.2 从RTL角度来看verilog中=和<=的区别

- 8.3 case和casez的区别

- 8.4 关于参数的传递与读取(paramter)

- 8.5 关于符号优先级

- 第9章 verilog中的一些语法使用

- 9.1 可综合的repeat

- 第10章 system verilog

- 10.1 简介

- 10.2 推荐demo学习网址

- 10.3 VCS在linux上环境的搭建

- 10.4 deepin15.11(linux)下搭建system verilog的vcs仿真环境

- 10.5 linux上使用vcs写的脚本仿真管理

- 10.6 system verilog基本语法

- 10.6.1 数据类型

- 10.6.2 枚举与字符串

- 第11章 tcl/tk的使用

- 11.1 使用Tcl/Tk

- 11.2 tcl基本语法教程

- 11.3 Tk的基本语法

- 11.3.1 建立按钮

- 11.3.2 复选框

- 11.3.3 单选框

- 11.3.4 标签

- 11.3.5 建立信息

- 11.3.6 建立输入框

- 11.3.7 旋转框

- 11.3.8 框架

- 11.3.9 标签框架

- 11.3.10 将窗口小部件分配到框架/标签框架

- 11.3.11 建立新的上层窗口

- 11.3.12 建立菜单

- 11.3.13 上层窗口建立菜单

- 11.3.14 建立滚动条

- 11.4 窗口管理器

- 11.5 一些学习的脚本

- 11.6 一些常用的操作语法实现

- 11.6.1 删除同一后缀的文件

- 11.7 在Lattice的Diamond中使用tcl

- 第12章 FPGA的重要知识

- 12.1 面积与速度的平衡与互换

- 12.2 硬件原则

- 12.3 系统原则

- 12.4 同步设计原则

- 12.5 乒乓操作

- 12.6 串并转换设计技巧

- 12.7 流水线操作设计思想

- 12.8 数据接口的同步方法

- 第13章 小项目

- 13.1 数字滤波器

- 13.2 FIFO

- 13.3 一个精简的CPU( mini-mcu )

- 13.3.1 基本功能实现

- 13.3.2 中断添加

- 13.3.3 使用中断实现流水灯(实际硬件验证)

- 13.3.4 综合一点的应用示例

- 13.4.5 使用flex开发汇编编译器

- 13.4.5 linux--Flex and Bison

- 13.4 有符号数转单精度浮点数

- 13.5 串口调试FPGA模板